A AMD demonstrou as vantagens de um layout de chip na primeira geração EPYC (Nápoles), mas nas gerações subsequentes o layout homogêneo foi substituído por um heterogêneo, com um chip separado responsável por todas as necessidades relacionadas às operações de E/S.

Foi o caso de Roma, foi o caso de Milão, Génova e Bérgamo, e agora é hora de ver o que mudou no EPYC 9005 (Turim) anunciado outro dia, e se isso será suficiente para consolidar mais uma vez o título de líder na área de criação de decisões de servidores multi-core.

Fonte: AMD

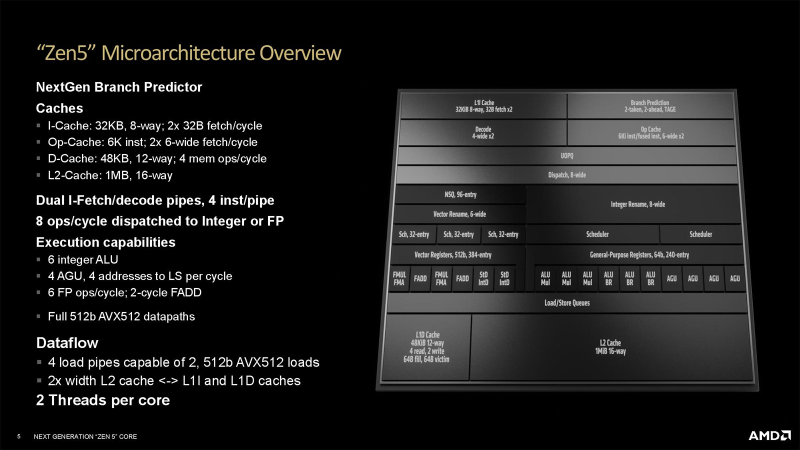

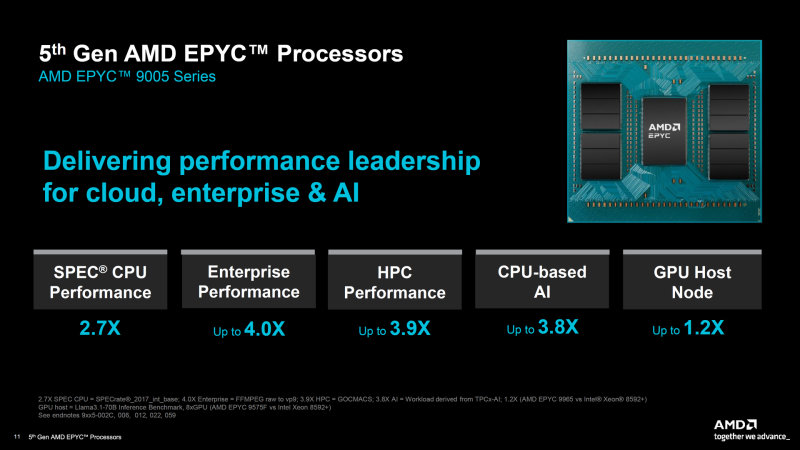

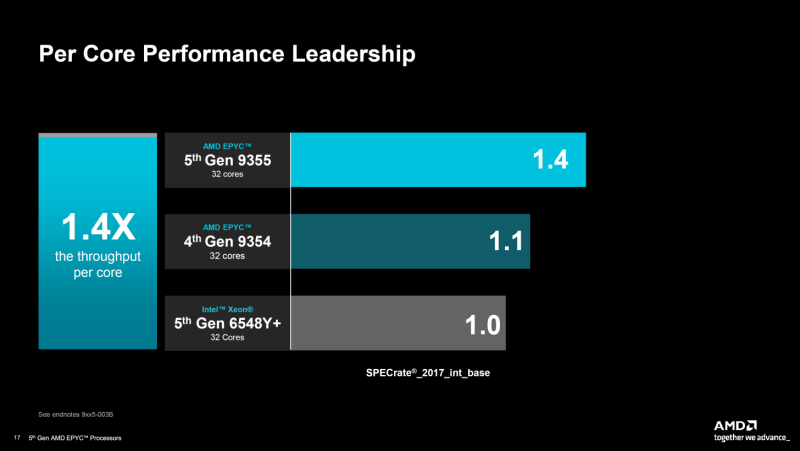

Em primeiro lugar, esta é, claro, a chegada da arquitetura de computação Zen de quinta geração na série EPYC, que já estreou há algum tempo nos processadores AMD Ryzen de classe consumidora. Como você sabe, no Zen 5, a AMD fez um bom trabalho ao aumentar a eficiência – o indicador IPC (o número de instruções executadas por ciclo de clock) aumentou cerca de 17%. Por trás disso estão mudanças bastante sérias na microarquitetura, que, no entanto, são de natureza evolutiva.

O núcleo Zen 5 recebeu uma nova unidade de previsão de ramificação, um agendador unificado, unidades de busca e decodificação de instruções foram divididas em dois clusters para otimizar o SMT (é interessante comparar com a abordagem da Intel, que está caminhando para abandonar completamente o SMT).

O cache de primeiro nível foi acelerado e aumentado em volume, as tabelas de tradução de endereços cresceram em tamanho e a própria parte computacional se expandiu com o aumento no número de instruções suportadas. Em particular, o Zen 5 implementa suporte total para AVX-512 com processamento de dados justo de 512 bits.

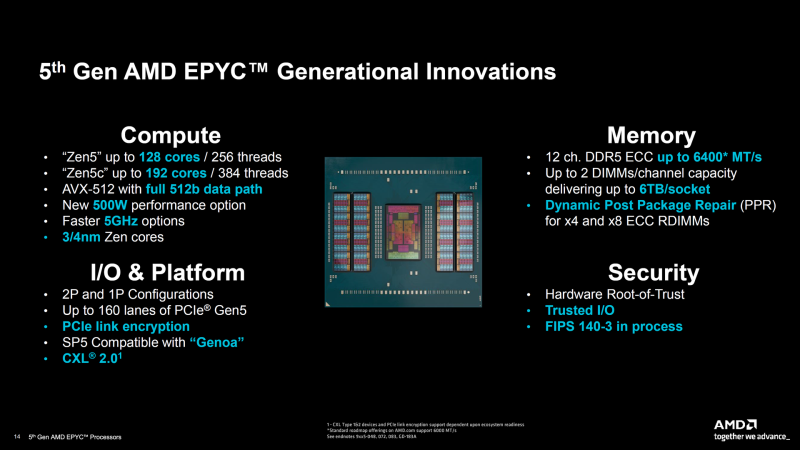

Mas voltemos ao novo EPYC 9005. A liderança do Intel Xeon 6 (Granite Rapids e Sierra Forest) em número de núcleos não durou muito: a AMD recuperou a liderança, guiada por uma fórmula simples: aumento de 50% em o número de núcleos + pacote térmico aumentado em 25% + transição para a arquitetura Zen 5/5c, mantendo a compatibilidade com o ecossistema de hardware existente.

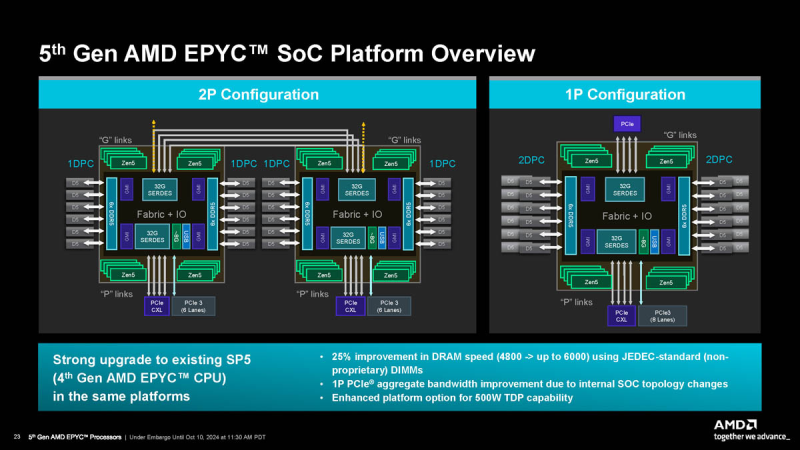

Assim como a geração anterior EPYC (Gênova e Bérgamo), os novos processadores Turin utilizam o soquete SP5 (LGA-6096), projetado para um subsistema de memória de 12 canais e 128 pistas PCI Express 5.0. No caso de um layout de placa-mãe com processador duplo, alguns destes últimos são usados para comunicação entre processadores.

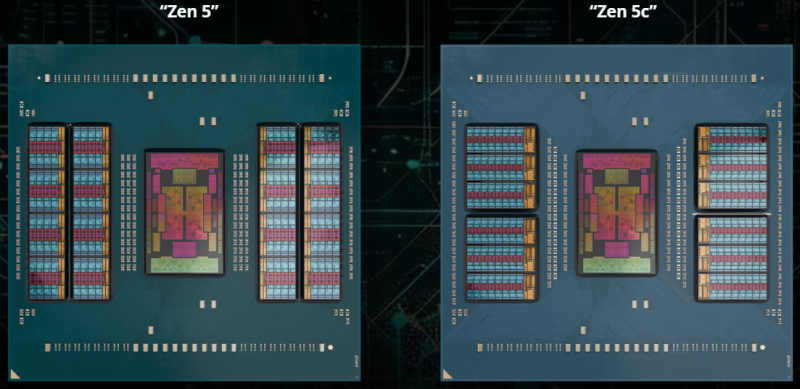

Curiosamente, desta vez um nome separado não é usado para a variante de alta densidade do processador: as versões EPYC 9005 têm diferentes layouts de chiplet CCD com núcleos Zen 5 e Zen 5c, bem como diferentes identificadores de modelo (00-0Fh e 10h -1Fh, respectivamente), mas possuem o mesmo codinome, embora exista também uma variante chamada Turin Dense.

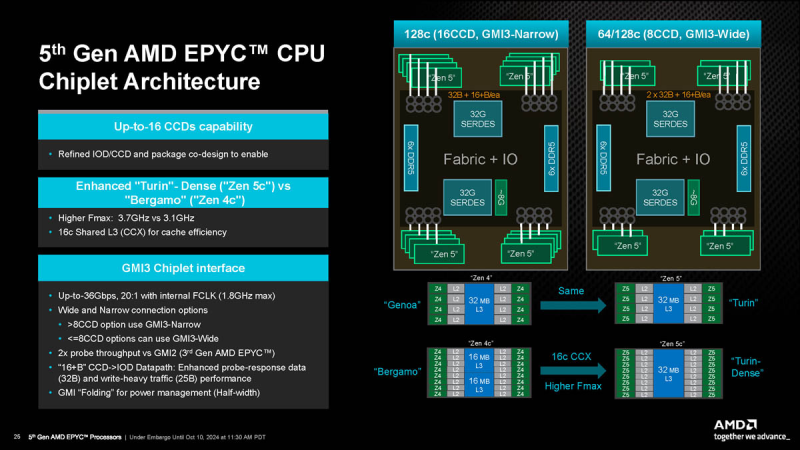

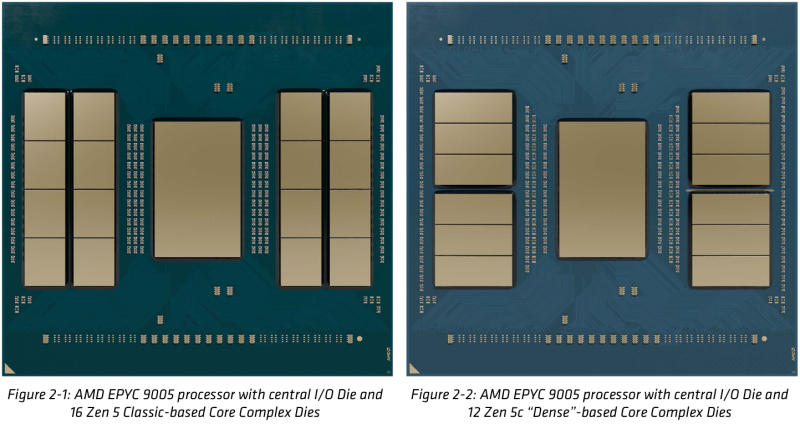

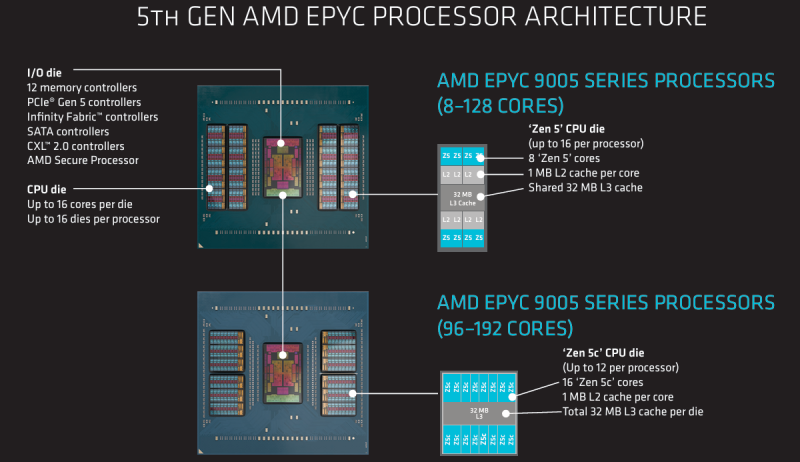

Informações publicadas anteriormente sobre 16 chips de oito núcleos para a versão clássica e 12 chips de dezesseis núcleos para a versão Turin de alta densidade foram confirmadas. Os chips são de fato agrupados em quatro e três blocos (quadrantes), respectivamente.

Os próprios chips foram transferidos para processos de fabricação TSMC de 4 e 3 nm, o que possibilitou outro aumento no número de núcleos. De acordo com este indicador, a versão de alta densidade do Turin até quebrou a barreira dos 128 núcleos, o que é a primeira vez para um processador x86.

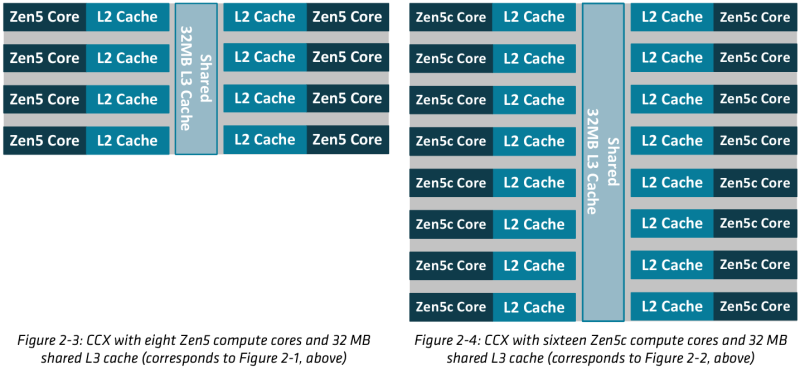

A estrutura interna do CCX tem diferenças significativas: na verdade, o CCX é definido por uma única seção de cache L3, e é o mesmo para as variantes baseadas em Zen 5 e Zen 5c e tem capacidade de 32 MB. Em outras palavras, cada núcleo Zen5c tem potencialmente menos cache (2 MB versus 4), mas esse é o preço para um layout mais denso.

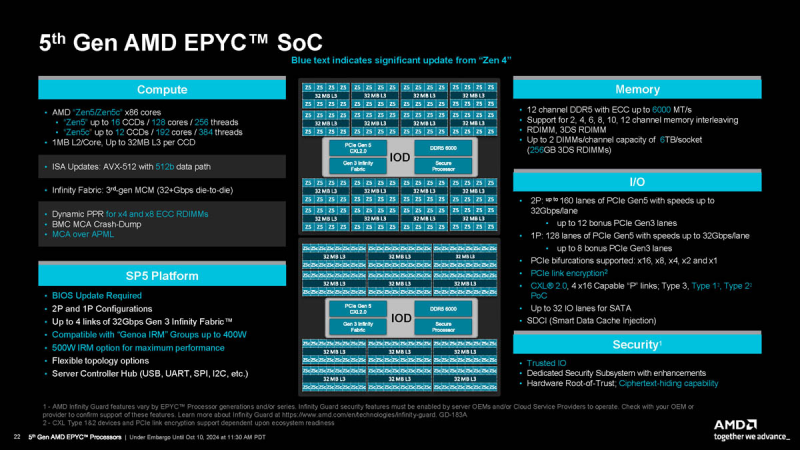

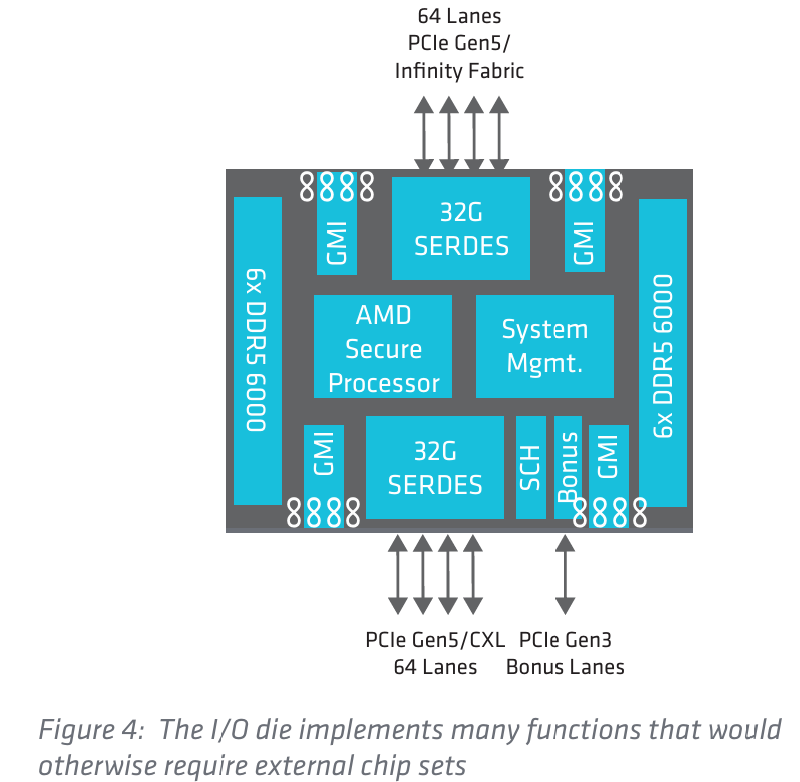

O bloco IOD (I/O Die) ainda é um, embora tenha sido seriamente redesenhado para suportar um número maior de CCDs conectados. A conexão é feita por meio de links GMI3, que operam na frequência de 1,8 GHz. Eles são duas vezes mais rápidos que o GMI2 usado na série de processadores EPYC 7003.

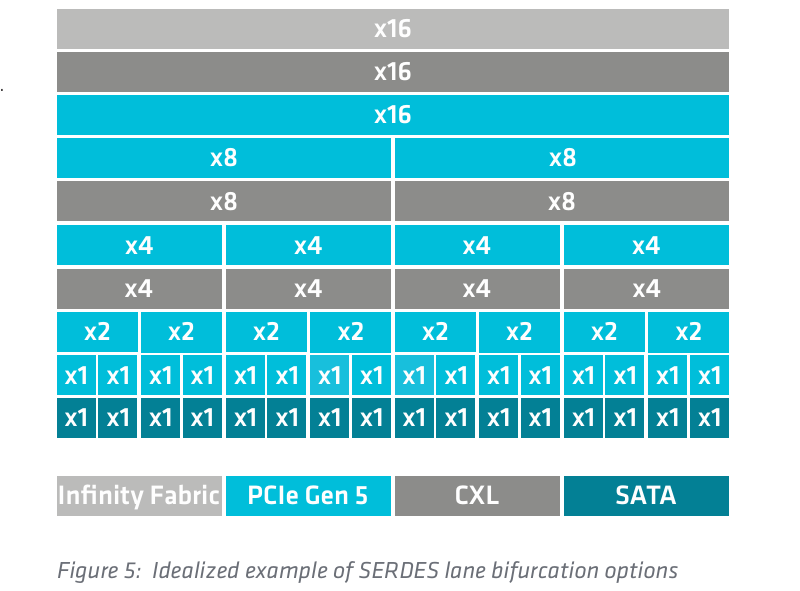

Existem dois modos de operação: GMI3-Narrow para configurações com 12 e 16 chiplets e GMI3-Wide para processadores com apenas 8 CCDs ativos (o throughput do CCD para o IOD dobra). Quatro links xGMI podem ser usados para trocar dados com um segundo processador no caso de uma configuração 2S. O novo IOD oferece flexibilidade para bifurcar linhas SerDes e atribuir funções específicas a elas.

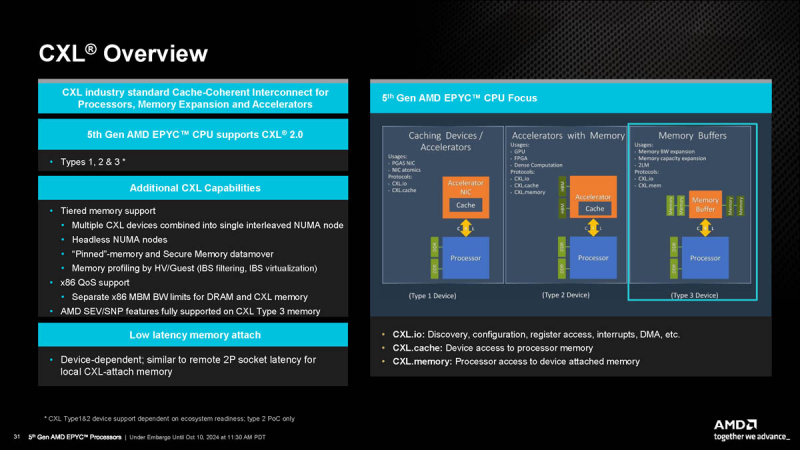

O módulo IOD fornece ao Turin suporte para 128 pistas PCI Express 5.0 no modo de processador único e até 160 no modo de processador duplo. Quatro links x16 podem ser usados como 64 pistas CXL 2.0 (Tipo 1, 2, 3) e até 32 linhas IO podem ser configuradas como interfaces SATA. A última interface está perdendo relevância rapidamente hoje, e seu suporte foi implementado pela AMD principalmente para compatibilidade intraplataforma.

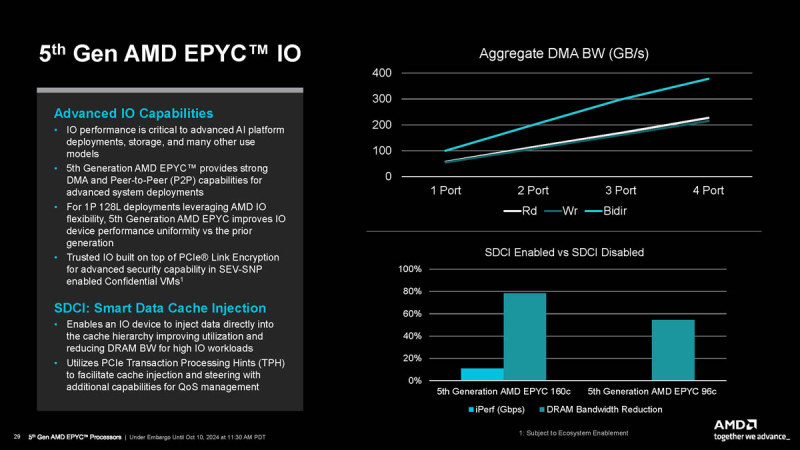

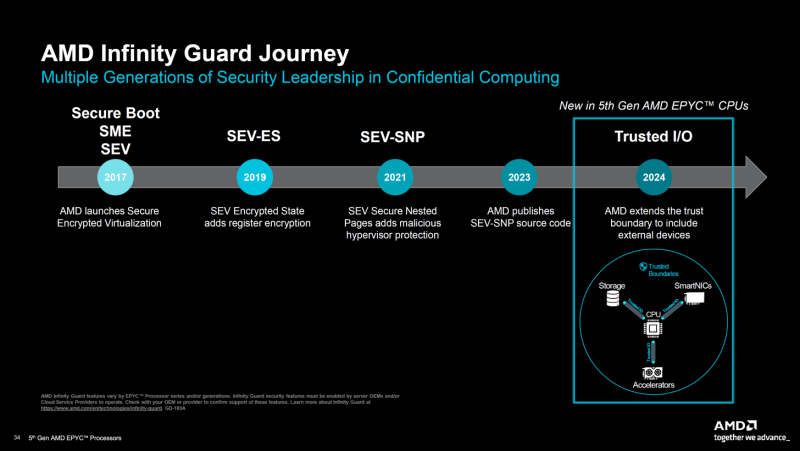

A AMD também tentou maximizar a eficiência dos subsistemas de E/S em princípio, entendendo a importância dos canais que conectam a CPU a todos os tipos de aceleradores na era da IA e do LLM. EPYC 9005 oferece suporte total a conexões DMA e P2P, enquanto a segurança não é esquecida: a criptografia de tráfego PCIe é implementada na estrutura do SEV-SNP.

Também é interessante a tecnologia SDCI, que permite que dispositivos de E/S gravem dados diretamente na hierarquia de cache, ignorando a DRAM, o que reduz a carga no subsistema de memória e aumenta potencialmente a eficiência da troca de dados entre o processador e os aceleradores.

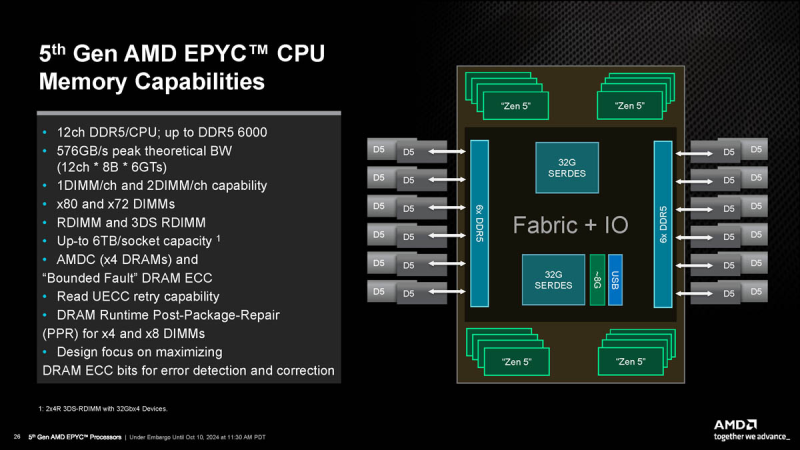

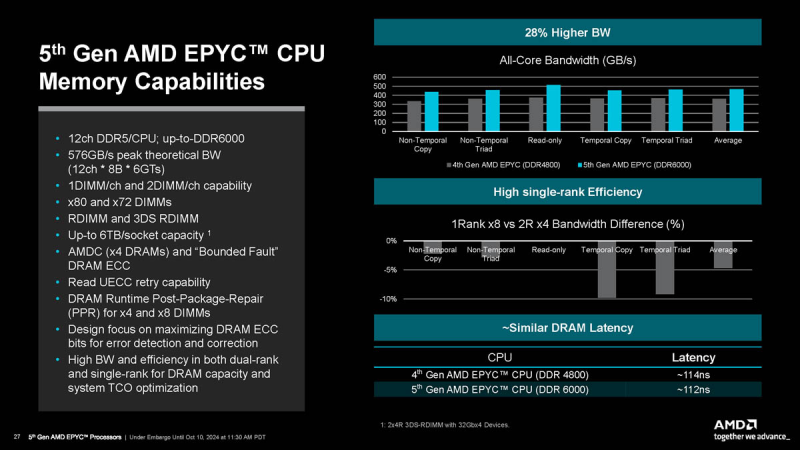

Nos processadores Xeon 6, a Intel superou seriamente a AMD em termos de parâmetros de subsistema de memória: até Sierra Forest recebeu suporte para DDR5-6400 (5200 em 2DPC), e Granite Rapids ainda suporta o novo MRDIMM DDR5-8800, recepção com 12 canais. Os processadores AMD EPYC estavam limitados a suportar, na melhor das hipóteses, DDR5-4800, embora com um número semelhante de canais.

Mas o advento de Turim restaura a paridade prática: ainda existem 12 canais de memória, mas a plataforma agora suporta DDR5-6000, e para algumas plataformas personalizadas a AMD permitirá suporte para DDR5-6400. EPYC 9005 não oferece suporte a produtos exóticos como MCRDIMM/MRDIMM em sua forma atual. Em vez disso, a empresa planeja permitir que futuros EPYCs suportem o novo padrão de memória assim que for ratificado pela JEDEC.

No entanto, mesmo sem levar em conta o aumento das frequências, que por si só poderiam proporcionar um aumento de 20 a 25% no rendimento, há inovações suficientes: os novos controladores de memória são significativamente mais eficientes que os antigos, suportam módulos de correção de erros x80 e x72, pode tentar ler novamente UECC, suporta 3DS RDIMM com capacidade total de 6 TB por processador.

O rendimento máximo pode atingir 576 GB/s, que é superior ao NVIDIA Grace (72 núcleos, 500 GB/s), mas inferior ao do Grace Superchip duplo (144 núcleos, 1 TB/s). A latência não aumentou em nada e é aproximadamente os mesmos 110 ns dos controladores de memória EPYC da geração anterior trabalhando com módulos DDR5-4800.

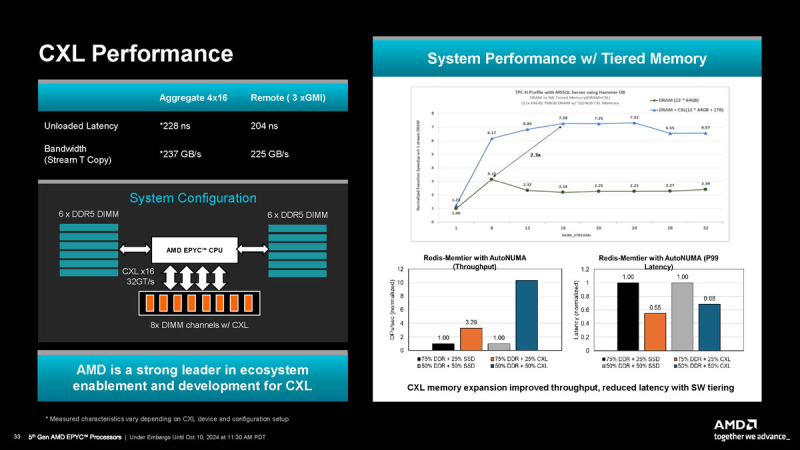

Conforme mencionado, o EPYC 9005 implementa totalmente suporte CXL 2.0 para todos os três tipos de dispositivos existentes, mas se concentra em trabalhar com dispositivos Tipo 3 como expansores de RAM. É fornecido suporte para níveis de hierarquia, capacidade de combinar dispositivos CXL em um domínio NUMA comum, funções QoS com compartilhamento de largura de banda para memória DRAM e CXL, etc. A AMD tentou garantir o melhor desempenho possível do CXL com latência mínima, mas apenas os testes podem mostrar quão bem essas inovações funcionam em comparação com, por exemplo, o Xeon Granite Rapids.

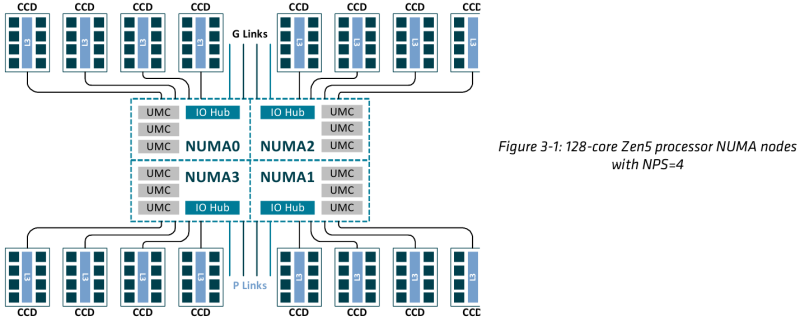

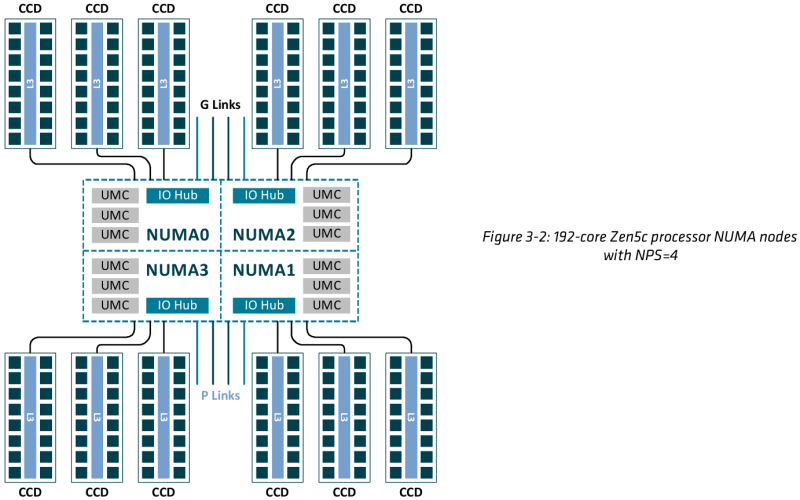

Quando se trata de NUMA, não podemos deixar de mencionar que EPYC 9005 pode operar em diferentes modos dependendo do valor NUMA Nodes Per Socket (NPS) no BIOS. Um valor 0 em um sistema de dois soquetes significa uma configuração monolítica com um domínio NUMA para todo o sistema. A memória opera no modo intercalado como um espaço de endereço único. Ambos os processadores têm acesso igual a toda a memória e a todos os dispositivos PCIe/CXL fisicamente conectados.

Um valor de 1 fornece dois domínios, 2 divide cada processador em dois domínios e 4 representa cada “quadrante” do processador como um domínio NUMA separado, incluindo 4 CCDs no Zen 5 e 3 CCDs no Zen 5c. A escolha da configuração depende do cenário de uso e do software específico utilizado.

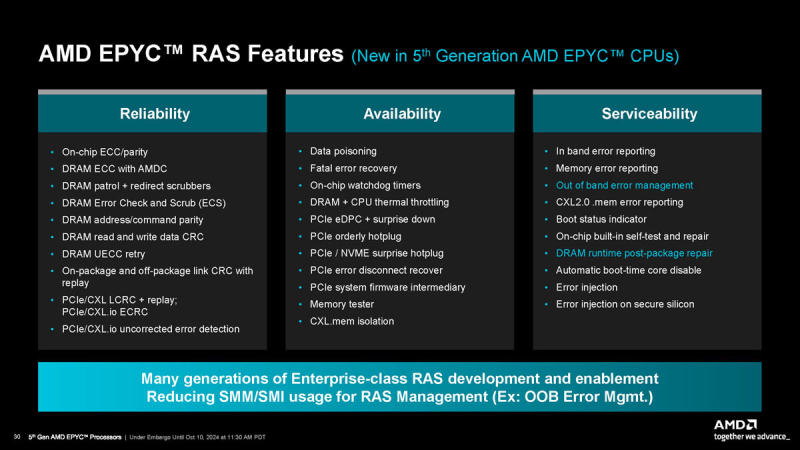

Também digno de nota é o conjunto ampliado de ferramentas de confiabilidade e estabilidade (RAS). Aos já implementados na geração anterior do EPYC, foi adicionado o processamento remoto de erros através de um canal dedicado (gerenciamento de erros fora de banda) e a substituição automática de células DRAM defeituosas por células de backup funcionando. A lista de recursos RAS suportados é ampla.

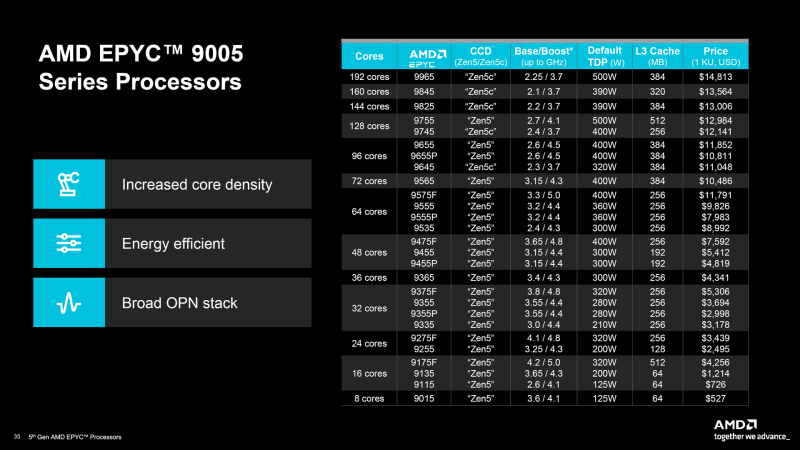

Ao contrário da Intel, a AMD apresentou 27 modelos EPYC 9005 de uma só vez, com o número de núcleos de 8 a 192. Deve-se notar imediatamente que os novos processos técnicos e a arquitetura aprimorada tiveram um impacto muito positivo na fórmula de frequência EPYC: se anteriormente a frequência no modo turbo raramente ultrapassava 4 GHz, então com o EPYC 9005 isso é normal.

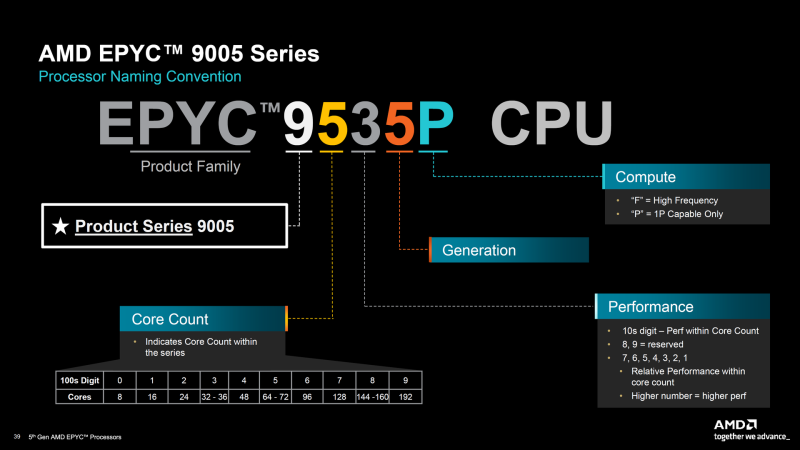

As únicas exceções são os modelos com núcleos Zen 5c, mas mesmo para eles esse parâmetro é de 3,7 GHz, que é acompanhado pelos pacotes térmicos correspondentes de 320–500 W. Observe que neste último caso é necessária uma atualização dos subsistemas de potência da plataforma, já que anteriormente o TDP máximo não ultrapassava 400 W. A nova série EPYC ainda inclui modelos individuais projetados para funcionar em sistemas de processador único que possuem o sufixo “P” em seus nomes;

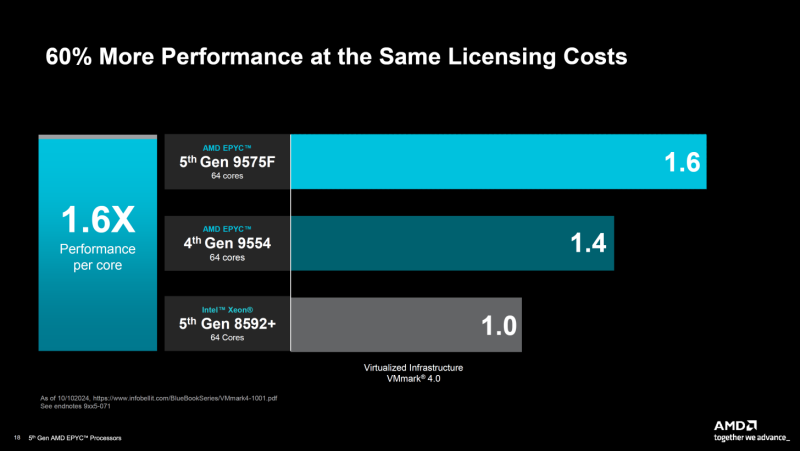

O sufixo “F” marca modelos com fórmula de frequência estendida, em que o limite inferior é de pelo menos 3,1 GHz e o limite superior se aproxima de 5 GHz. Esses processadores também possuem a quantidade máxima de cache L3. Juntamente com as frequências, isso torna o EPYC 9005F a escolha ideal para cenários com licenciamento de software por núcleo.

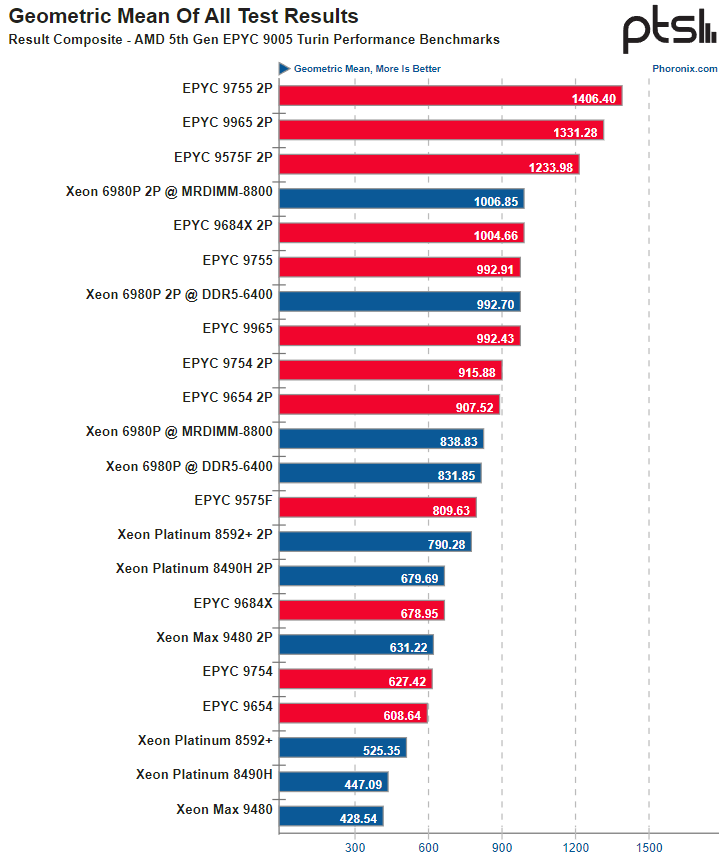

Os primeiros resultados dos testes de novos processadores de servidor AMD já foram publicados online: por exemplo, os revisores do recurso Phoronix conseguiram testar três novos produtos de uma vez – EPYC 9755 (128 núcleos Zen 5, turbo de 4,1 GHz), 9575F (64 Zen 5 núcleos, turbo de 5 GHz) e 9965 (192 núcleos Zen 5c, turbo de 3,7 GHz). Os resultados são impressionantes: a combinação do Zen 5 em forma de servidor com velocidades de clock aumentadas funcionou, e os novos produtos da AMD ocuparam firmemente os primeiros lugares em quase todas as categorias.

Fonte: Phoronix

Em alguns locais, por exemplo, no teste OpenSSL, o Turin Dense (EPYC 9965) teve um desempenho excelente, pois está à frente do Intel Xeon 6700E não apenas no número de núcleos (192 versus 144), mas também nos próprios núcleos, apesar otimização de densidade, é uma implementação completa do Zen 5, e não uma versão simplificada da “grande arquitetura”, como é o caso dos Intel E-cores. Como resultado, os três primeiros lugares pertencem às soluções AMD, e apenas o quarto lugar foi conquistado por um sistema com Xeon 9680P equipado com módulos MRDIMM-8800 de alta velocidade. Ele, equipado com o DDR5-6400 usual, foi capaz de funcionar adequadamente apenas contra um único EPYC 9755. Para um sistema de processador duplo com EPYC 9755, a diferença em relação a uma plataforma semelhante baseada em Granite Rapids foi em média de 40%.

Quanto ao EPYC 9965 de alta densidade, ele está 45% à frente do conjunto de processador duplo baseado no carro-chefe EPYC 9754 Bergamo, apesar do menor número de núcleos (192 versus 256). A nova arquitetura e um aumento significativo nas frequências de clock tiveram efeito. O consumo de energia dos novos produtos da AMD, é claro, não é tão impressionante quanto o do Intel Xeon 6700E (Sierra Forest), mas não muito pior, e o EPYC 9755, apesar do monstruoso pacote térmico de 500 W, ainda acabou sendo ser mais econômico que o Xeon 6980P. Seu teto de consumo de energia era de fato de 500 Watts, enquanto o carro-chefe da Intel consumia quase 550 Watts em seu pico.

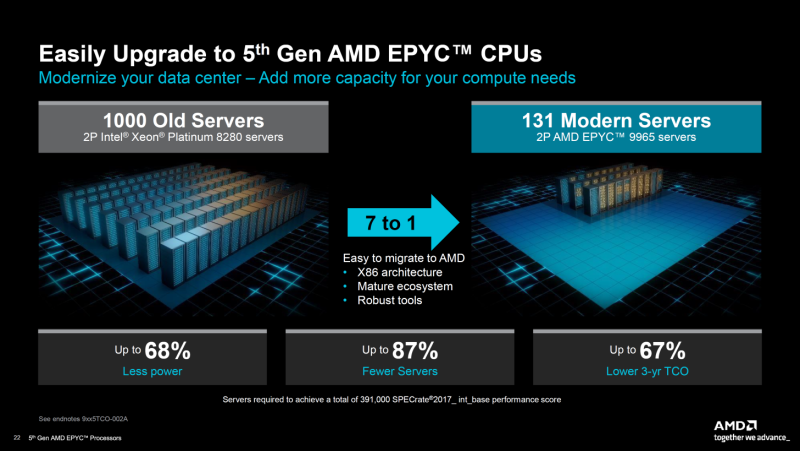

Ao mesmo tempo, a placa Intel bate mesmo onde as “azuis” sempre foram invencíveis – agora a AMD também tem suporte total para AVX-512, bem como uma resposta de 192 núcleos ao Xeon 6700E de 144 núcleos. O investimento de capital para a conversão da infra-estrutura de EPYC de quarta geração para quinta geração pode ser relativamente pequeno. Na maioria dos casos, a tarefa se limita a atualizar um novo BIOS e substituir os próprios processadores. Os fabricantes de equipamentos para servidores receberam com entusiasmo os novos produtos da AMD e, aparentemente, a participação da empresa no mercado de servidores continuará a crescer.

Dos trunfos que ainda estão nas mãos da Intel no momento, só podemos citar a presença de blocos aceleradores específicos, bem como suporte para extensões matemáticas de matriz AMX. Em alguns cenários, como servidores de telecomunicações, isso ajudará o Xeon a manter sua posição, mas na maioria das outras cargas de trabalho, o EPYC Turin parece muito melhor. Além disso, os novos processadores de servidor AMD são visivelmente mais baratos que as soluções Intel.