Hoje, diante de nossos olhos, uma séria mudança de paradigma está ocorrendo no mundo da fabricação de processadores: os desenvolvedores estão se afastando de arquiteturas unificadas de uso geral e soluções monolíticas em direção à modularidade e ao uso ativo de aceleradores de hardware específicos. É claro que a Arm não ficou de lado – no evento OCP Global Summit 2023, a empresa falou sobre a nova iniciativa Arm Total Design.

Esta iniciativa deverá ajudar tanto os criadores de novos processadores, acelerando o processo de desenvolvimento e reduzindo o seu custo, como os proprietários de grandes infra-estruturas informáticas. Estes últimos estão cada vez mais inclinados para a especialização e diferenciação nas novas gerações de arquitecturas de processadores, mas também esperam eficiência energética, respeito pelo ambiente e o menor custo total de propriedade possível.

Fonte das imagens aqui e abaixo: Arm

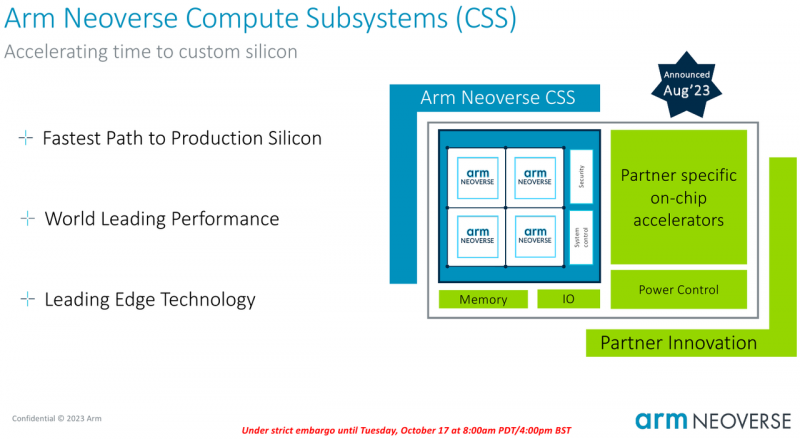

A iniciativa Arm é baseada na plataforma de processador Arm Neoverse Compute Subsystem (CSS), anunciada em agosto no HotChips 2023. Neoverse CSS N2 (Genesis) é um conjunto pronto de soluções Arm IP, incluindo núcleos de processador, sistema de interconexão interna, subsistemas de memória, E/S, gerenciamento de energia, mas deixando espaço para a integração de desenvolvimentos de parceiros – vários motores, aceleradores, etc.

Na verdade, estamos falando de processadores quase prontos que não requerem um desenvolvimento demorado da parte do processador do zero e todas as atividades associadas a esse processo – verificação, testes em FPGA, validação de projeto e muito mais. De acordo com Arm, essa abordagem pode economizar aos desenvolvedores até 80 anos-homem de trabalho de engenharia.

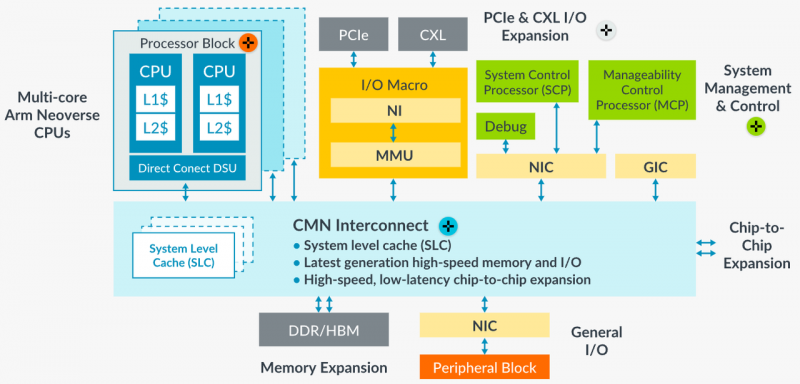

O design do Neoverse CSS N2 é bastante flexível: o processador final pode incluir de 24 a 64 núcleos Arm operando na faixa de frequência de 2,1-3,6 GHz. Há um cache de instruções e dados de 64 KB, mas os volumes dos caches L2 e L3 são configuráveis e podem atingir 1 e 64 MB, respectivamente. Os núcleos implementam o conjunto de instruções Arm v9 e contêm duas unidades de vetor SVE2 de 128 bits. Há suporte para instruções específicas para tarefas de IA e criptografia.

O subsistema de memória pode ter até 8 canais DDR5 e os recursos de E/S incluem 4 blocos de 16 pistas PCIe ou CXL. Também é possível combinar dois chips CSS N2 em um único pacote, o que dá até 128 núcleos por chip. A rede mesh Neoverse CMN-700 é usada como interconexão interna.

O design Neoverse CSS N2 também apresenta núcleos de suporte Cortex-M7. Eles funcionam como parte dos blocos System Control Processor (SCP) e Management Control Processor (MCP), ou seja, controlam o funcionamento do array computacional principal, sendo inclusive responsáveis por sua alimentação e frequências de clock.

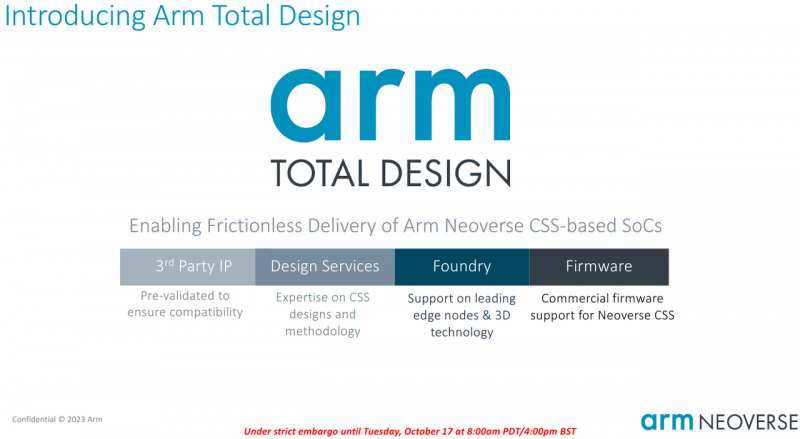

A iniciativa Arm Total Design expande o escopo do Neoverse Compute Subsystem: estamos falando sobre a criação de um ecossistema completo que garanta a comunicação eficaz entre os parceiros do programa Neoverse CSS e forneça-lhes ferramentas IP completas e EDA, criadas com o participação de Cadence, Rambus, Synopsys e outros.

Implica também o apoio dos principais fabricantes de silício e desenvolvedores de firmware, em particular AMI. Os participantes do projeto já incluem empresas como ADTechnology, Alphawave Semi, Broadcom, Capgemini, Faraday, Socionext e Sondrel. Espera-se o suporte da Intel Foundry Services e TSMC, permitindo-nos falar sobre a implementação eficaz das tecnologias AMBA CHI C2C e UCIe necessárias para soluções multi-chip.

Estando unidos sob o mesmo teto da iniciativa Arm Total Design, esse conglomerado de desenvolvedores e fabricantes líderes de microeletrônica e software de sistema será capaz não apenas de criar novos processadores no menor tempo possível, mas também de responder com flexibilidade aos desafios de o mercado de data centers e HPC, fornecendo chips com suporte para tecnologias e aceleradores populares.

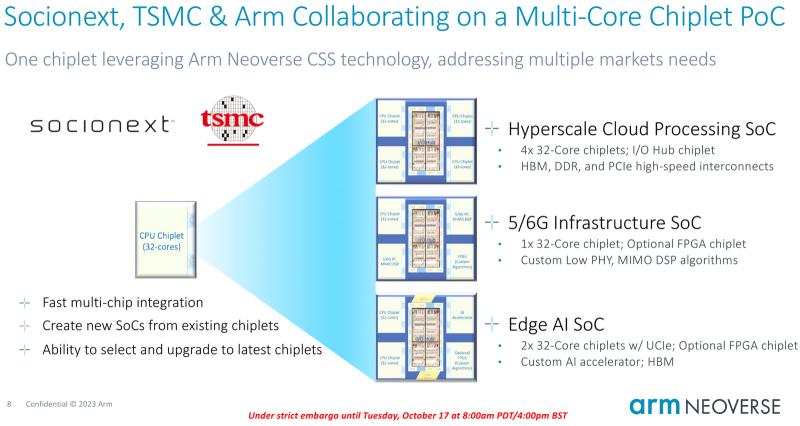

Um exemplo é o projeto conjunto da Arm, Socionext e TSMC, no qual está em andamento o desenvolvimento de um processador chiplet universal, que em diversas opções de layout será procurado por hiperscaladores, fornecedores de infraestrutura 5G/6G e desenvolvedores de sistemas periféricos de IA.