Os componentes de computação de alto desempenho atuais são difíceis de imaginar sem um layout espacial sofisticado que permita que a Lei de Moore permaneça em vigor à medida que a litografia de silício se aproxima de seus limites físicos. A TSMC apresentou o kit de ferramentas 3Dblox 2.0, que simplificará o design de tais componentes avançados.

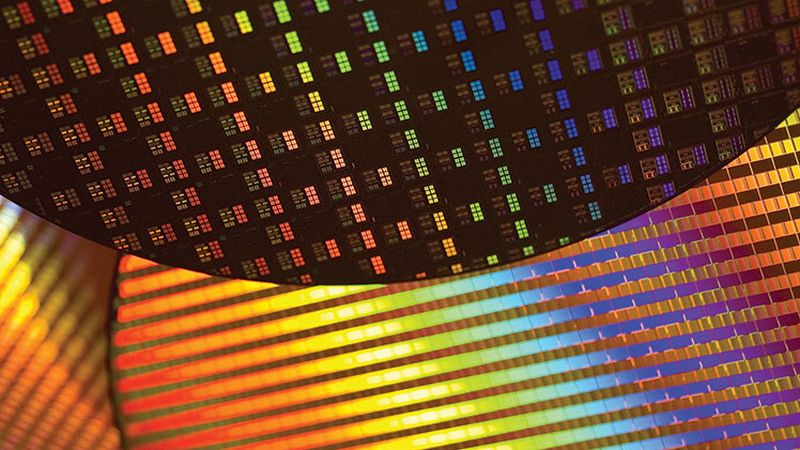

Fonte da imagem: TSMC

A primeira versão do padrão aberto para design de elementos com layout espacial complexo foi apresentada pela TSMC em outubro do ano passado e agora foi refinada e aprimorada. A nova versão do 3Dblox possui um recurso de reaproveitamento de chips e a capacidade de avaliar preliminarmente o nível de consumo de energia e dissipação de calor do chip projetado. Tudo isso deve melhorar a eficiência do projeto de chips com layouts espaciais complexos.

Fornecedores de software especializado apoiaram a iniciativa e, como resultado, o Comitê 3Dblox incluiu representantes da Ansys, Cadence, Siemens e Synopsys. A sua participação garante que as ferramentas de desenvolvimento automatizado de componentes propostas sejam mutuamente compatíveis com as soluções TSMC.

A 3DFabric Alliance mais ampla conta agora com 21 empresas membros. A cooperação entre os membros da aliança concentra-se em três áreas principais. Primeiramente, são discutidos e implementados métodos avançados para integração de chips de memória como o mesmo HBM3. Em segundo lugar, estão em curso desenvolvimentos para melhorar os métodos de trabalho com substratos. Em terceiro lugar, os membros da aliança interagem entre si na área de métodos de teste de produtos acabados. Idealmente, a TSMC e seus parceiros pretendem alcançar um aumento de dez vezes no desempenho da linha de teste de chips.