Os analistas da TrendForce esperam que, em 2023 e 2024, o mercado veja um aumento na demanda por memória HBM de alto desempenho. Nesse contexto, os especialistas prevêem um aumento na produção de chips usando tecnologias avançadas de embalagem em 30-40%.

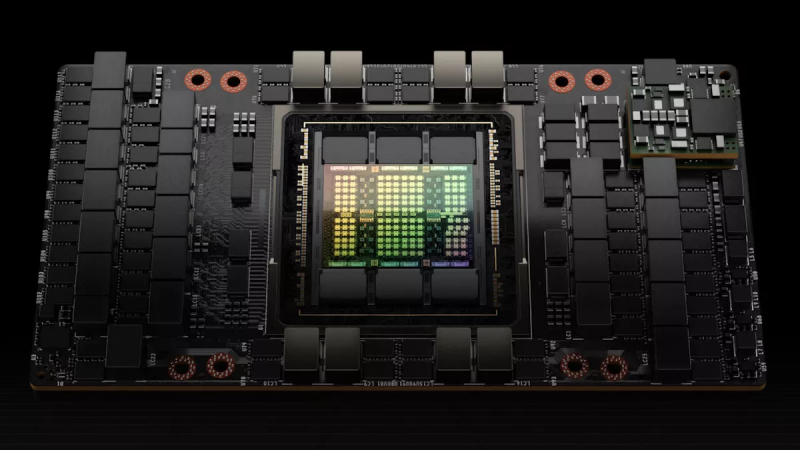

Fonte da imagem: NVIDIA

A explosão na popularidade de aplicativos generativos de IA, como chatbots, levou a mudanças significativas no mercado de servidores em 2023. Os principais provedores de serviços de TI ocidentais, como Microsoft, Google, AWS, bem como as empresas chinesas Baidu e ByteDance, estão investindo pesadamente em servidores avançados de alto desempenho para treinar e otimizar seus modelos de IA.

Para aumentar a eficiência dos servidores AI e aumentar a largura de banda de seus subsistemas de memória, os principais fabricantes de chips AI, como NVIDIA, AMD e Intel, estão introduzindo ativamente memória HBM de alto desempenho em seus produtos. Em particular, os aceleradores NVIDIA A100 e H100 oferecem até 80 GB de memória HBM2e e HBM3. Em seu acelerador Grace Hopper mais avançado, o fabricante usa pilhas de memória HBM com capacidade aumentada em 20% (até 96 GB). Os aceleradores MI300 da AMD também são equipados com memória HBM3. Os mesmos modelos MI300A oferecem 128 GB de memória, enquanto o MI300X mais avançado oferece até 192 GB de memória especificada. Como parte da expansão de sua infraestrutura de IA, espera-se que o Google fortaleça sua cooperação com a Broadcom e inicie a produção do chip acelerador de inteligência artificial TPU até o final deste ano.

A TrendForce prevê que a quantidade total de memória HBM usada em aceleradores de IA, incluindo NVIDIA H100 e A100, AMD MI200 e MI300 e Google TPU, será de 290 milhões de gigabytes, um aumento de 60% em relação ao ano anterior. Em 2024, esse crescimento permanecerá em 30% ou mais.

Em IA e HPC, também há uma demanda crescente por tecnologias avançadas de empacotamento de chips. A escolha predominante para a fabricação de chips de IA para servidores é a tecnologia Chip on Wafer on Substrate (CoWoS) da TSMC. A tecnologia de embalagem CoWoS inclui dois estágios: CoW e oS. No estágio CoW, vários microcircuitos lógicos (processadores centrais e gráficos, ASICs), bem como a memória HBM, são combinados entre si. No estágio oS, os elementos do conjunto CoW são instalados no substrato do chip. Posteriormente, é formado um SoC, que é integrado à placa-mãe do servidor, com base no qual é criada uma plataforma de IA com equipamentos de rede, um subsistema de memória, fontes de alimentação e outros componentes.

Os especialistas preveem que, no cenário de forte demanda por chips avançados de IA em geral e memória HBM em particular, a produção mensal de chips usando a tecnologia de embalagem CoWoS da TSMC aumentará para 12 mil unidades até o final de 2023. Desde o início de 2023, a demanda por CoWoS cresceu quase 50%, impulsionada pela alta popularidade dos aceleradores NVIDIA A100 e H100, bem como servidores AI baseados neles. Ao mesmo tempo, diante do crescente interesse em CoWoS da AMD, Google e outras empresas, o número de linhas gratuitas para a produção de chips com CoWoS provavelmente será limitado no segundo semestre deste ano, dizem os analistas. A alta demanda por CoWoS continuará até pelo menos 2024 e, portanto, espera-se um aumento nas capacidades disponíveis correspondentes em 30-40% no próximo ano, levando em consideração a disponibilidade do equipamento necessário.

Se a alta demanda por tecnologias de IA continuar, é provável que a mesma NVIDIA considere o uso de embalagens avançadas alternativas para a produção de chips. Tais, por exemplo, são oferecidos pela Amkor e Samsung.