A luta pela eficiência energética dos semicondutores clássicos está atingindo um novo patamar. A startup israelense NeoLogic explicou em termos simples o atraso dos processos de fabricação de chips CMOS e propôs a mudança para o processo CMOS+, que está livre de muitas das deficiências de seu antecessor. Isso é especialmente importante no contexto da ampla introdução da inteligência artificial e das redes neurais, que consomem toda a energia livre, onde quer que ela esteja.

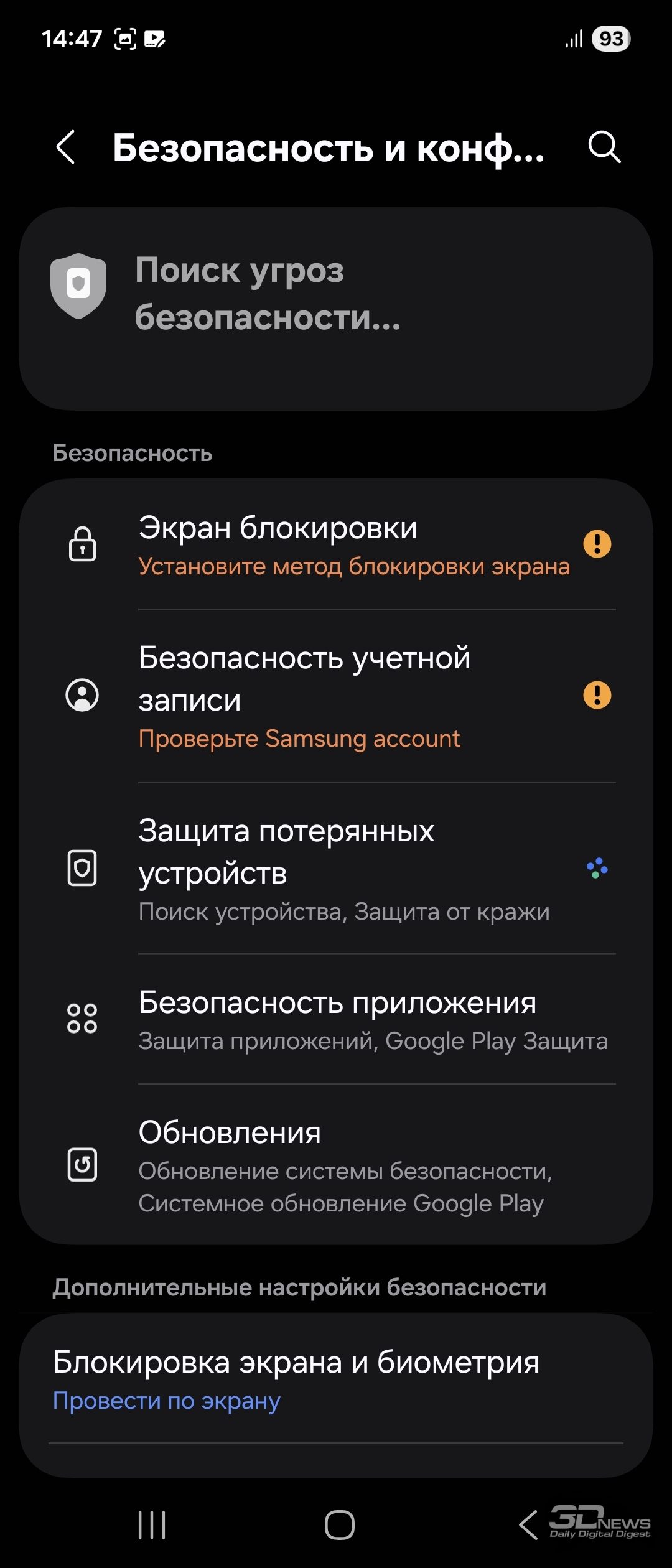

Manual NeoLogic. Fonte da imagem: NeoLogic

As ideias da NeoLogic encontraram eco nos corações dos investidores. A empresa recentemente levantou US$ 10 milhões para desenvolver processadores de servidor com eficiência energética, cuja primeira versão pretende apresentar até o final deste ano, e já em 2027 a desenvolvedora pretende iniciar a implementação em massa do novo paradigma em servidores e outras soluções.

Então, o que a NeoLogic oferece em vez de uma estrutura complementar de metal-óxido-semicondutor, que é uma matriz de elementos feitos de pares de transistores fortemente acoplados com diferentes condutividades?

Os circuitos CMOS foram inventados no início da década de 60 do século passado e se tornaram a salvação da eletrônica na década de 90 e em todos os anos subsequentes. Devido ao posicionamento próximo de muitos pares de transistores de polaridades diferentes no cristal, eles proporcionam alta velocidade, têm atrasos menores e se distinguem pelo consumo mínimo em modo estático. Sua principal desvantagem é a área relativamente grande no cristal devido à “duplicação” do número de portas. Os engenheiros da NeoLogic propuseram corrigir isso introduzindo portas simplificadas ao mundo, que eles chamaram de “elementos com complexidade reduzida” (portas de complexidade reduzida).

A NeoLogic afirma que sua abordagem pode reduzir o tamanho dos processadores em 40%, reduzindo pela metade seu consumo de energia. Quanto menos transistores em um chip, menos energia ele consome. Além disso, com certos projetos de circuito, o número de transistores que utilizam a tecnologia CMOS+ pode ser reduzido em até três vezes. Mas isso não é tudo. A NeoLogic tem mais dois trunfos na manga: “portas de nível único” e uma nova arquitetura de buffer.

Em condições normais, os chips CMOS têm um número limitado de entradas para processamento de dados. Aumentá-las para paralelizar cálculos complica significativamente o projeto e aumenta o consumo de energia. A NeoLogic afirma que sua tecnologia CMOS+ alcança um paralelismo sem precedentes devido às portas de transistor de estágio único. Segundo a empresa, essas portas podem processar significativamente mais dados em paralelo do que um circuito CMOS padrão, consumindo menos energia.

Por fim, os buffers no circuito CMOS+ são otimizados para eficiência energética. Em particular, a NeoLogic propõe aumentar a área do buffer (que surpresa!).

A NeoLogic foi fundada em 2021 pelo CEO Avi Messica e pelo CTO Ziv Leshem. A empresa está confiante de que os processadores baseados em CMOS+ serão adequados para trabalhar com modelos de inteligência artificial. A empresa acredita que sua tecnologia permitirá trabalhar no modo de tomada de decisão com menor consumo de energia do que placas de vídeo.