Os maiores fabricantes terceirizados de chips estão, de uma forma ou de outra, migrando para a fonte de alimentação no verso do chip, pois permite otimizar o layout do chip e melhorar seu desempenho. A Samsung Electronics espera que sua tecnologia de fonte de alimentação traseira de 2 nm reduza a área da matriz em 17%.

Fonte da imagem: Samsung Electronics

Como relata a TrendForce, citando a mídia sul-coreana, as declarações correspondentes na quinta-feira foram feitas por Lee Sungjae, vice-presidente da equipe de desenvolvimento PDK da Samsung Foundry, durante seu discurso aos parceiros da empresa. Além de reduzir a área da matriz em 17%, a transição para a fonte de alimentação no verso dos chips de 2 nm aumentará seu desempenho em 8% e melhorará a eficiência energética em 15%.

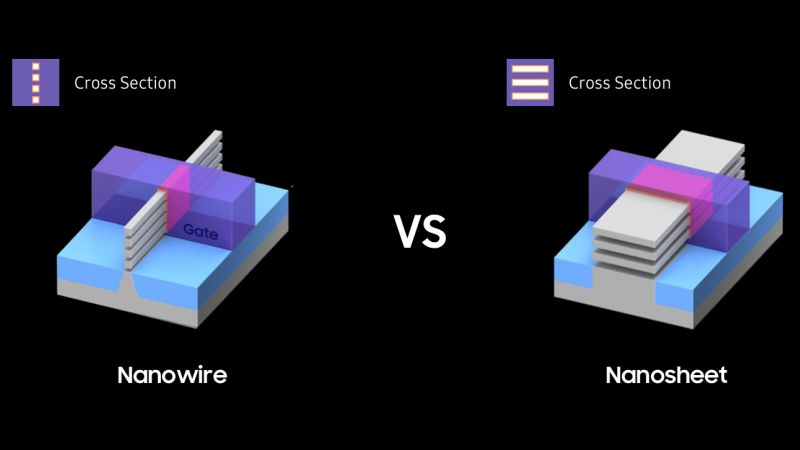

Lembremos que a concorrente Intel planeja usar tecnologia semelhante na produção em massa de chips com tecnologia 20A antes do final deste ano em sua implementação recebeu a designação PowerVia; A taiwanesa TSMC implementará uma solução semelhante chamada Super PowerRail como parte da tecnologia A16 em 2026. Neste caso, o primeiro utilizará uma nova estrutura de transistores RibbonFET, e o segundo introduzirá transistores com “nanofolhas”.

A tecnologia mais recente da Samsung é chamada MBCFET. A empresa coreana pretende utilizar a segunda geração da estrutura de transistor com porta envolvente (GAA) a partir do atual semestre, e também utilizá-la no âmbito do processo de 2 nm que será dominado posteriormente. A própria tecnologia SF3 aumenta o desempenho do chip em 30%, melhora sua eficiência energética em 50% e também reduz a área da matriz em 35% em comparação com o GAA de primeira geração. Quando combinada com a fonte de alimentação traseira (BSPDN), esta estrutura de transistor proporcionará benefícios adicionais.