A AMD registrou uma patente descrevendo o recurso do projeto de aglomerado GPU (de vários cristais). Em particular, em uma nova patente chamada Chiplet Active Bridge com cache integrado, um barramento ativo com memória de cache integrado é descrito. Pode-se assumir que estamos falando sobre a evolução da tecnologia de cache infinito, que apareceu pela primeira vez nas placas de vídeo da série Radeon RX 6000.

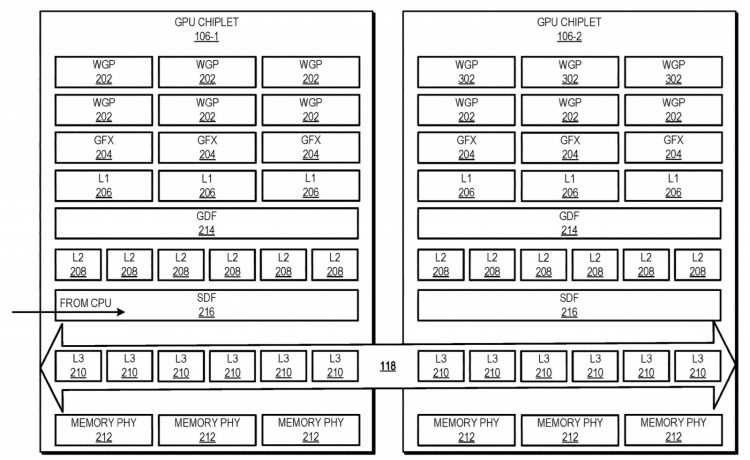

A ideia da AMD é atribuir a interface que conecta as coleções selecionadas de GPU separadas entre si, incluindo a função de memória de cache de terceiro nível. Lembre-se de que na GPU atual com base nos arquitetos RDNA 2, a função do 3º nível é realizada pelo cache infinito.

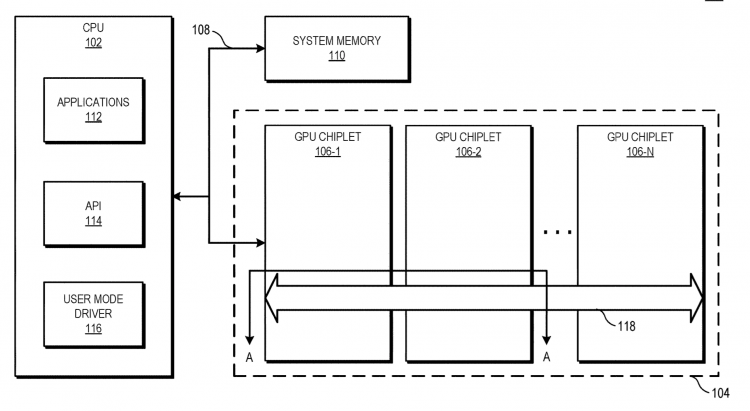

Um diagrama de blocos mostrando o sistema de processamento usando o barramento ativo conectando os chips GPU

A AMD em patente explica que qualquer interação entre o chiplot será realizada por meio de um barramento ativo que será necessário para acessar canais de memória em cristais de processadores gráficos individuais. Em vez de confiar em kershes separados de cada aplauso AMD, propõe usar o ativo ativo do pneu como um cache monolítico do processador gráfico. Em outras palavras, a memória do cache será endereçada como um único registro.

Diagrama de blocos da hierarquia da memória do cache dos chiplots GPU, ativo ativo combinado

A última patente da AMD, como anterior, que foi relatada em janeiro deste ano, indica que a empresa realiza um estudo ativo do uso de gpus multiculturais no futuro. É verdade que não é claro se é apenas sobre os aceleradores computacionais da nova geração na arquitetura de ADNc ou AMD considera a possibilidade de usar o design do aglomerado também em placas de vídeo consumidor na arquitetura RDNA.

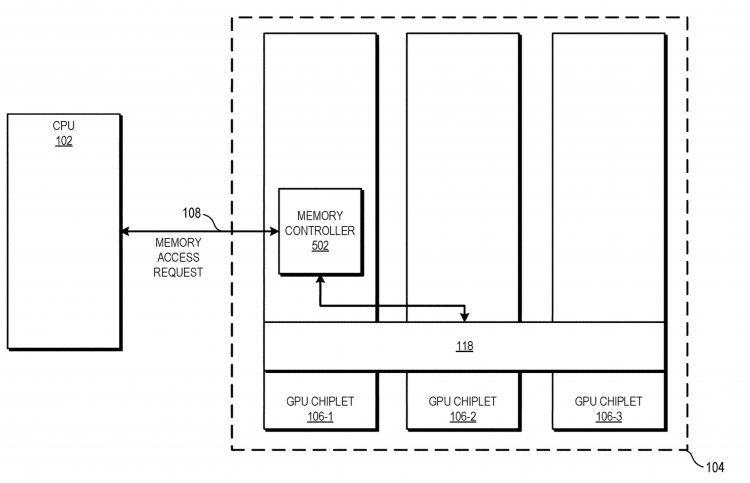

Bloqueando o diagrama de usar uma configuração de três merda

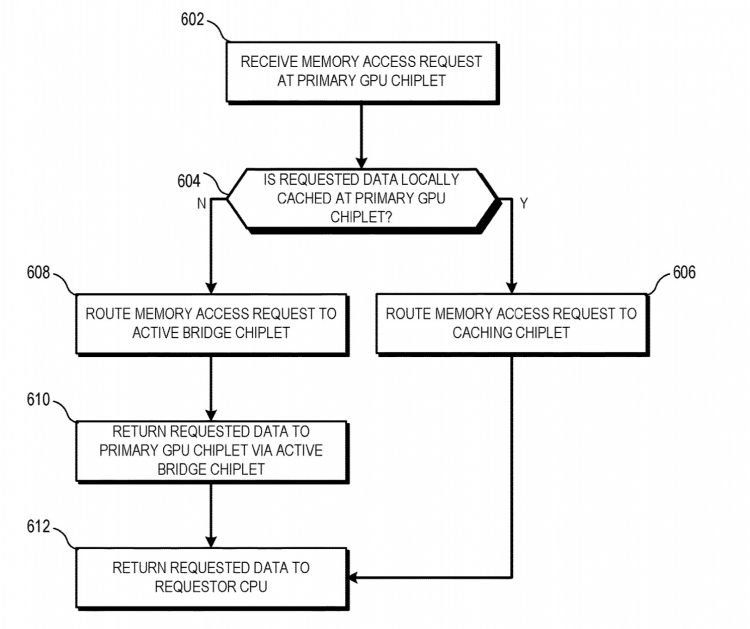

Esquema de troca de dados entre chiplots

A propósito, não apenas a AMD funciona nessa direção. Por exemplo, esse desenvolvimento é NVIDIA e Intel. O primeiro é um enorme XE-HPC multicultural, no segundo – GH100 (Hopper), que também é atribuído à Assembléia Multicultural (MCM).