O diretor executivo da Intel Pat Gelsinger (Pat Gelsinger) como parte da Intel Unleashed: Engenharia O evento futuro, falou sobre a implementação do projeto para desenvolver um acelerador Ponte Vecchio, destinado a utilização em sistemas de computação de alto desempenho (HPC).

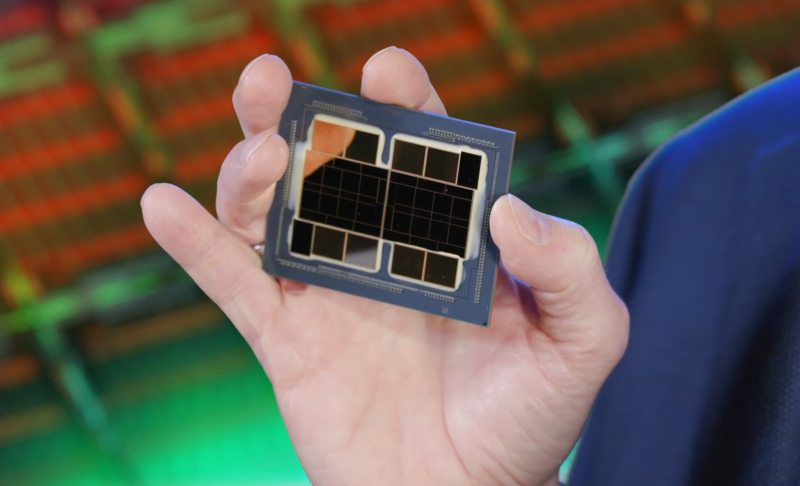

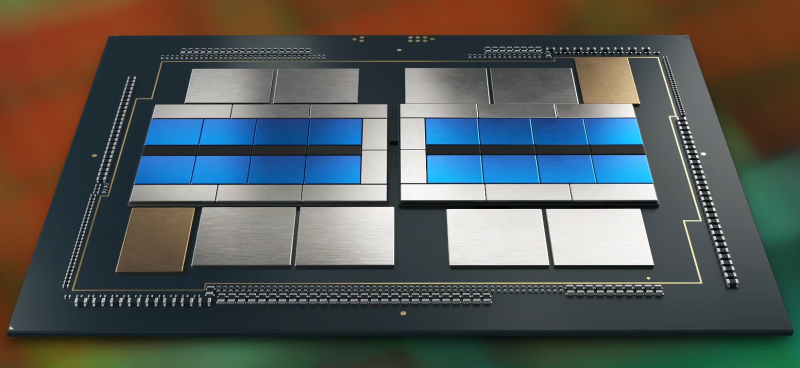

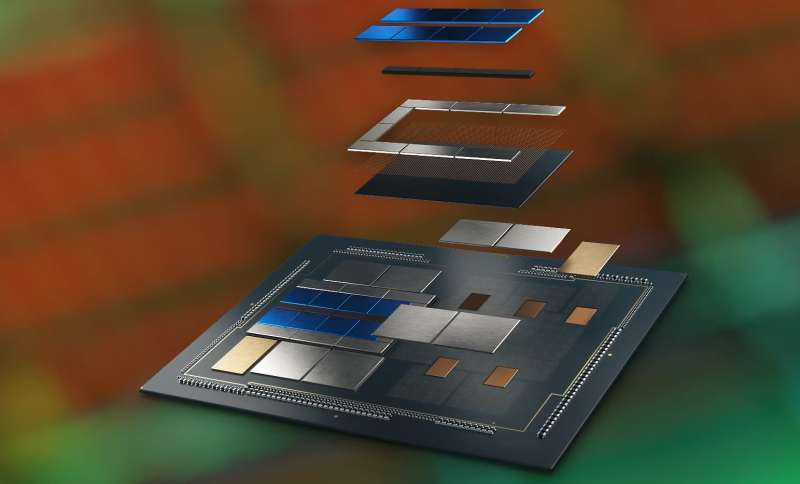

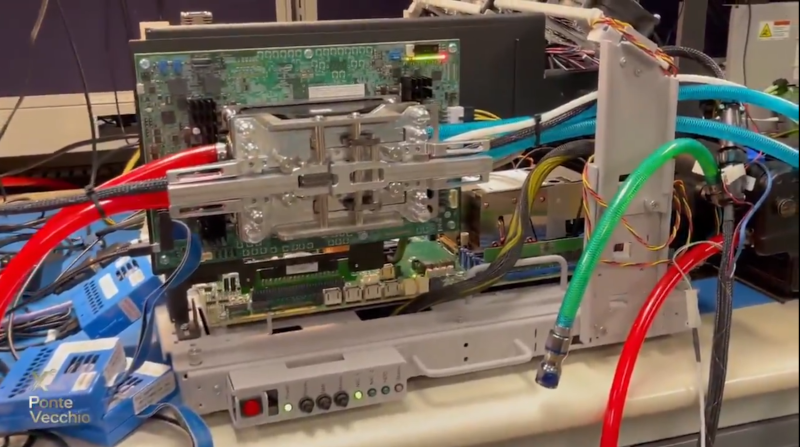

Note-se que um pouco mais de dois anos da existência do projeto, a Intel conseguiu alcançar resultados notáveis. Em particular, um processador experiente de amostra de trabalho já foi criado. O Sr. Gelcinger durante o desempenho mostrou esse produto. O processador tem um design “telhado” com 47 elementos, que é perfeitamente visível nas imagens publicadas.

A produção usa tanto o layout 3D de Foveros e as conexões da EMIB. O número total de transistores usados excede 100 bilhões. Também é relatado que a solução fornece desempenho em um só papa. Mas não especificando qual precisão é sobre.

Para comparação: AMD MI100 Peak FP64-desempenho é 11,5 TFLLOPS (e duas vezes maior para FP32), e a NVIDIA A100 é 9,7 TFLFs para FP64 e 19,5 TFLFs para FP32. Para outros formatos (BFloat16, FP16, INT4 ou INT8), esses valores são muitas vezes mais do que ambos os aceleradores.

Os processadores gráficos Ponte Vecchio serão usados no Tandem Xeon com o nome do código da Sapphire Rapids. A Ponte Vecchio, em particular, fará parte do supercomputador Aurora para o Laboratório Nacional de Argon do Departamento de Energia dos EUA. Complete a criação deste sistema está programado para o final deste ano.