As interfaces estão se tornando uma parte crítica das soluções de vários chips em um único pacote. Uma vez que os chips são espaçados pelo substrato, os barramentos que os conectam devem ter a maior largura de banda possível, latência mínima e baixo consumo de energia. Hoje, há uma dúzia dessas interfaces abertas e proprietárias. E o mais original deles, talvez, foi oferecido pela Global Unichip Corp, por trás da qual está a TSMC.

Placa de teste GLink e amostra de engenharia

Muitas das interfaces para pacotes de vários chips usam conversores SerDes como porta de extremidade do barramento. Este é um elemento inalterado de quase todas as interfaces clássicas, que transformam um conjunto de dados paralelo em uma sequência para transmissão em um conjunto limitado de linhas e faz a transformação reversa na outra extremidade (receptora) das linhas.

Global Unichip Corp (GUC) propõe abandonar o SerDes como um fenômeno obsoleto. Em vez disso, GUC oferece sua própria interface GLink (GUC multi-die interLink), e a TSMC está preparada para incorporar GLink em pedidos de clientes em pacotes de vários chips de chips de alto desempenho, por exemplo, em SoCs para smartphones emblemáticos e não apenas.

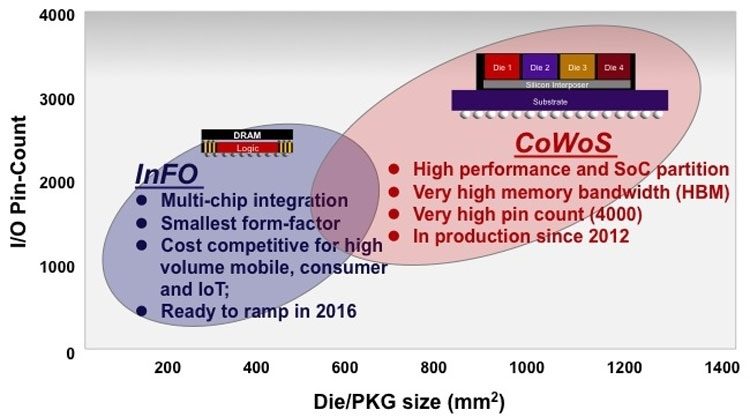

A TSMC praticou e está pronta para fornecer simulações da interface GLink para pacotes de vários chips, como InFO_oS e CoWoS para cristais de 7 nm. Argumenta-se que o GLink é mais benéfico para uso para esses pacotes TSMC com múltiplos cristais de até 2500 mm2. A nova interface oferece comunicação full-duplex sem erros entre matrizes em um pacote com largura de banda de 0,7 Tbps por mm de interface. Ao mesmo tempo, o consumo é de apenas 0,25 pJ / bit (0,25 W por 1 Tbit / s no modo full duplex).

De acordo com os resultados obtidos, o consumo de energia do GLink para cada 10 Tbps de tráfego full-duplex é 15-20 W menor do que no caso do uso de SerDes. Isso se deve principalmente ao fato de que os SerDes têm um valor de consumo constante independente do tráfego, e o consumo de GLink depende da quantidade de dados transferidos. Portanto, em média, sob cargas normais, a substituição do GLink por SerDes para conectar os cristais em pacotes promete uma economia de energia impressionante – até 20 vezes.

Dois métodos avançados de empacotamento de vários chips da TSMC

Finalmente, a GLink desenvolveu e está preparando um pacote de licenciamento de interface GLink para o processo de 5nm da TSMC e futuros 3nm. No primeiro caso, a taxa de câmbio aumentará para 1,3 Tbit / s por 1 mm da interface, e no segundo – para 2,7 Tbit / s, e tudo isso sem aumentar o consumo para a transmissão de cada bit de dados. Para tecnologia de processo de 5 e 3 nm, as soluções estarão disponíveis no próximo ano.

Em relação à proposta de abandonar o SerDes usual por causa do GLink, gostaria de dizer que agora é a hora de abandonar o usual. ASICs e chips especiais para aprendizado de máquina e IA estão se espalhando a uma velocidade tremenda. Comparados aos processadores clássicos, eles são tão incomuns e fazem você pensar de uma nova maneira e trabalhar de uma nova maneira. E isso, se você pensar sobre isso, é simplesmente maravilhoso. A indústria da computação há muito está moralmente estagnada. Há muito que falta um bom pontapé.