Nos últimos vinte anos, a computação e as comunicações têm migrado para interfaces ópticas. Isto já aconteceu nas linhas de comunicação de backbone, mas ainda está paralisado nos data centers e no nível das comunicações entre chips e entre componentes em computadores. Idealmente, o sinal deve vir imediatamente do processador na forma de pulsos ópticos e então ser enviado para o chip vizinho ou para racks vizinhos, para o corredor e até mesmo para outros lugares. A IBM escolheu esse caminho.

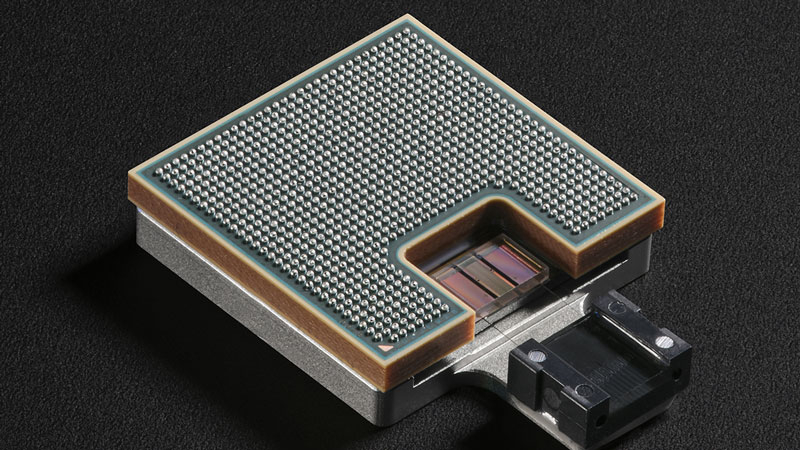

Slot CPO para instalação de um “cabo” óptico externo no chip. Fonte da imagem: IBM

A óptica se compara favoravelmente ao cobre (conexões condutoras) por seu peso leve, baixo custo, baixa interferência (ruído), alta velocidade de transmissão, baixo consumo de energia e, em geral, permite aumentar o rendimento sem aumentar o consumo de energia. A capacidade de usar linhas de comunicação óptica já está incluída em todos os padrões Ethernet mais recentes, bem como nos padrões PCIe. A Intel chegou mais perto de integrar linhas ópticas em processadores (aceleradores) com sua plataforma Light Peak. E embora a Intel tenha parado de desenvolver esta plataforma há muito tempo, a ideia não morreu e hoje continua na nova interface óptica Intel OCI (Open Compute Project Interconnect Link).

Hoje é a vez da IBM anunciar um avanço na direção de interfaces ópticas integradas em processadores. Tal como a Intel, a óptica integrada da IBM tem as suas raízes nos esforços fotónicos de silício que ambas as empresas iniciaram há mais de 20 anos. A nova interface integrada da IBM é chamada de óptica co-packaged (CPO). Literalmente, isso se traduz como óptica “co-packed” ou “combinada” – um canal adicional de transmissão de dados. Ele não substitui a fiação da placa-mãe e os cabos dentro do computador e entre os racks, mas os complementa com uma interface de alta velocidade e baixo consumo de energia.

Uma fibra óptica PWG (guia de onda óptica de polímero) barata foi selecionada como condutor de luz para a interface CPO. A empresa apresentou um protótipo funcional da interface (plataforma) com fibra óptica PWG de 50 mícrons de espessura e está pronta para escaloná-la para fibras ópticas com espessura inferior a 20 mícrons. As especificações da interface CPO permitem a troca de dados entre chips, placas e racks ou, mais simplesmente, trabalhar em distâncias de alguns centímetros a centenas de metros.

Se a solução proposta pela IBM for adotada e adotada pela indústria, ela reduzirá o custo de escalonamento de plataformas generativas de IA, reduzindo o consumo de energia em mais de cinco vezes em comparação com interconexões elétricas de médio porte, ao mesmo tempo em que aumentará o comprimento dos cabos de interconexão em data centers de um a centenas de metros.

Você também pode esperar um treinamento mais rápido de modelos de IA, permitindo que os desenvolvedores treinem grandes modelos de linguagem (LLMs) cinco vezes mais rápido do que usando interfaces com fio convencionais. A tecnologia CPO pode reduzir o tempo necessário para estudar um LLM padrão de três meses para três semanas. Isso também proporcionará ganhos de desempenho através do uso de modelos maiores e mais GPUs, o que reduzirá o tempo de inatividade do hardware.

Finalmente, a tecnologia CPO melhorará significativamente a eficiência energética dos data centers, economizando energia equivalente ao consumo anual de 5.000 residências nos EUA por treinamento de modelo de IA.

«À medida que a IA generativa exige mais energia e recursos computacionais, os data centers devem evoluir, e a óptica combinada pode torná-los mais promissores, disse Dario Gil, vice-presidente sênior e diretor de pesquisa da IBM. “Com esta inovação, os chips de amanhã transmitirão dados da mesma forma que os cabos de fibra óptica transmitem informações de e para data centers, inaugurando uma nova era de comunicações mais rápidas e resilientes, capazes de lidar com as cargas de trabalho de IA do futuro.”

Os pesquisadores da IBM forneceram informações detalhadas sobre a nova interface em um artigo publicado no arXiv.org. Novas estruturas ópticas de alta densidade de largura de banda, combinadas com a transmissão de múltiplos comprimentos de onda em um único canal óptico, aumentarão potencialmente o rendimento chip a chip em até 80 vezes o das interconexões elétricas.

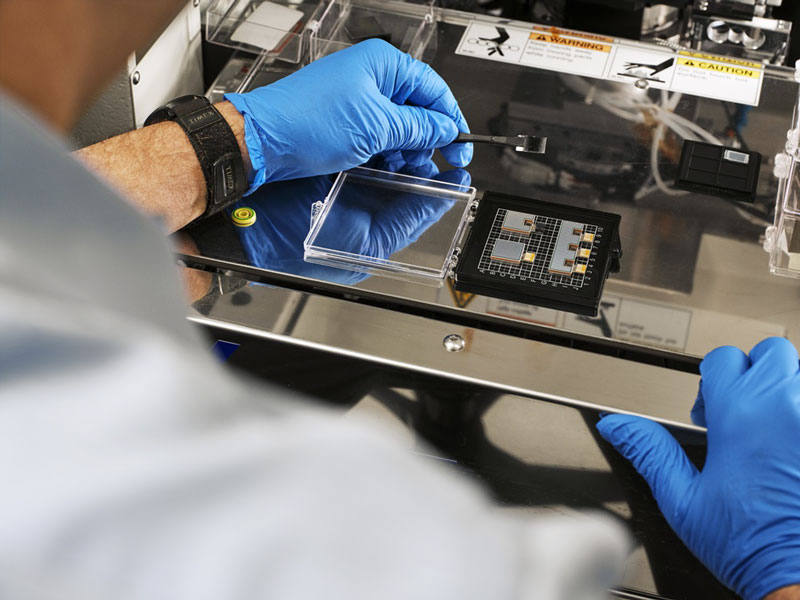

Testando interfaces ópticas IBM

A plataforma experimental passou em todos os testes de estresse necessários para produção. Os componentes foram submetidos a alta umidade e temperaturas variando de -40°C a +125°C, além de testes de resistência mecânica para confirmar que as conexões ópticas poderiam flexionar sem quebrar ou perder dados. Além disso, os pesquisadores demonstraram a tecnologia PWG com passo de 18 mícrons. A combinação de quatro blocos PWG com esta etapa permitirá conectar até 128 canais. Em última análise, isso fornecerá densidades de transmissão de até 10 Tbit/mm².