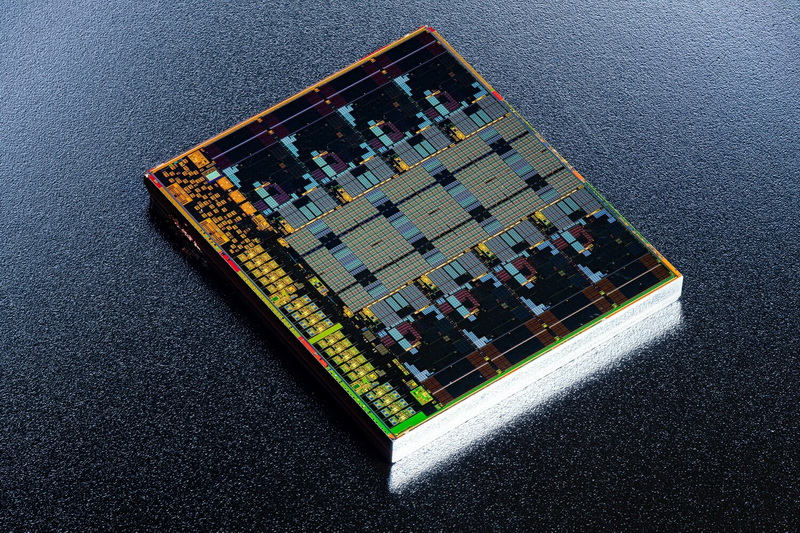

Os entusiastas da tecnologia realizaram uma desmontagem completa de um dos processadores da série Ryzen 9000 (Granite Ridge) e compartilharam imagens altamente detalhadas da matriz CCD (com núcleos Zen 5) e cIOD (entrada-saída) dos novos processadores.

Fonte da imagem: X / @FritzchensFritz

A embalagem dos novos chips é semelhante à embalagem dos antecessores do Ryzen 7000 (Raphael). Dependendo do modelo, o chip pode conter um ou dois chips CCD de oito núcleos, bem como uma matriz de entrada-saída (cIOD), localizada na parte central da placa do processador. O novo Ryzen 9000 emprestou o cristal cIOD de seus antecessores. Assim, a AMD conseguiu reduzir os custos de desenvolvimento de novos chips. Os cristais CCD com núcleos Zen 5 são fabricados usando a tecnologia de processo TSMC N4P 4nm.

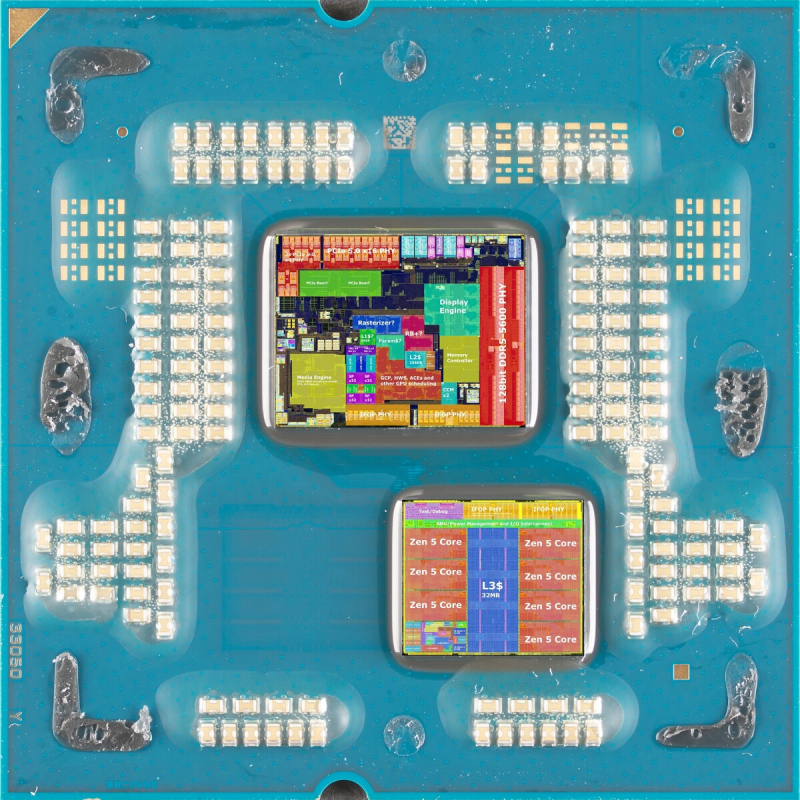

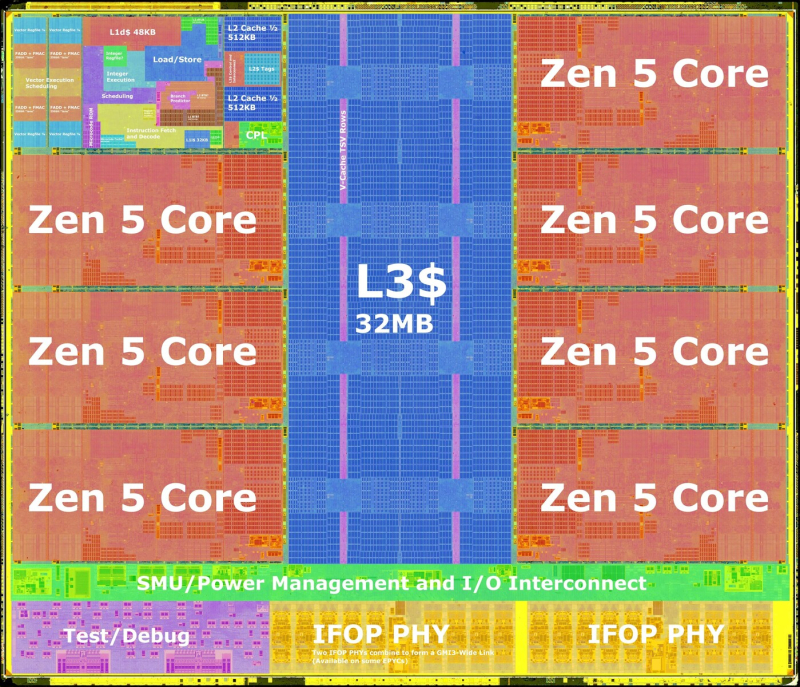

Os núcleos nos processadores CCD Granite Ridge estão localizados mais próximos uns dos outros do que nos processadores CCD Raphael Zen 4. Cada CCD Granite Ridge contém 8 núcleos Zen 5 de tamanho normal, cada um com 1 MB de cache L2. Na parte central do CCD estão 32 MB de memória cache L3, distribuídos entre os núcleos. Outros componentes do CCD são o controlador de controle SMU (System Management Unit) e a implementação física do barramento Infinity Fabric over Package (IFoP), que é necessário para conectar os chips CCD e cIOD.

Unidade CCD com núcleos Zen 5 de processadores Ryzen 9000

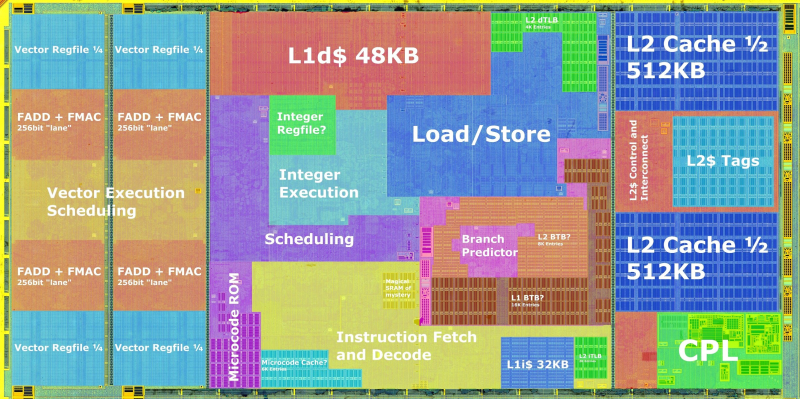

Cada núcleo Zen 5 é maior que o Zen 4 (fabricado usando tecnologia de processo TSMC N5) devido ao uso de uma unidade FPU com suporte nativo para dados de 512 bits para o AVX-512. O Vector Engine está localizado na borda do núcleo. Isso faz sentido, pois a FPU é o componente mais quente do núcleo da CPU. Na outra extremidade do núcleo, mais próximo do cache L3 compartilhado, existem dois blocos de cache L2 de 512 KB. A AMD dobrou a largura de banda e a associatividade deste cache em comparação com o Zen 4.

Diagrama central do Zen 5

A região central do Zen 5 contém 32 KB de cache L1I, 48 KB de cache L1D, Integer Execution Engine e a parte de entrada do pipeline do processador com uma unidade de busca e decodificação de instruções e uma unidade de predição (Branch Prediction Unit),. cache e agendador de microoperações (Scheduler).

O cache L3 na parte central da matriz CCD de 32 MB possui fileiras de TSVs (vias de silício) que servem como base para uma possível “colagem” com uma matriz de cache 3D V-Cache adicional. O die 3D V-Cache de 64 MB pode ser conectado diretamente ao barramento circular CCD interno usando esses TSVs.

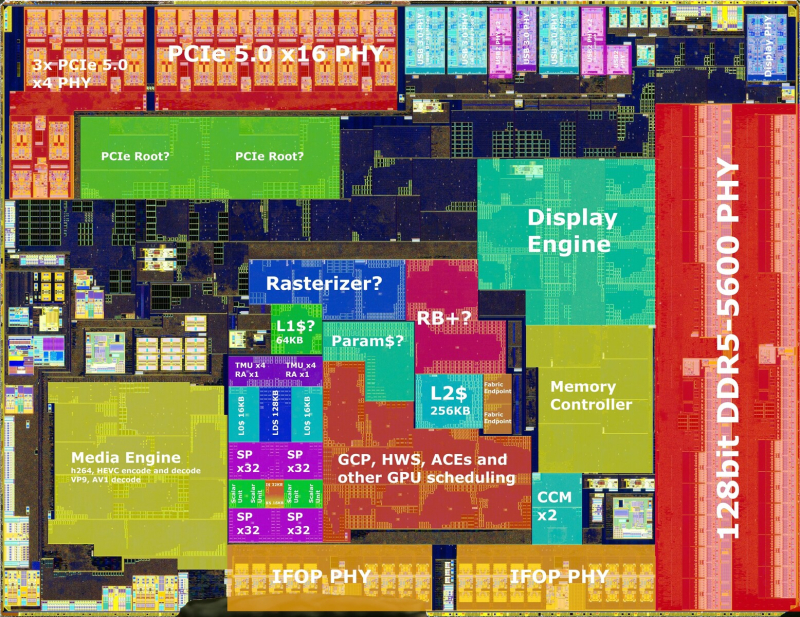

O cristal cIOD nos novos processadores é produzido usando a tecnologia de processo TSMC N6 6nm. Aproximadamente 1/3 de sua área é ocupada pela unidade iGPU integrada e seus componentes adjacentes, como o mecanismo multimídia e o mecanismo de exibição.

Bloco cIOD

O iGPU, como antes, é baseado na arquitetura gráfica RDNA 2 e está equipado com apenas um grupo de processadores de grupo de trabalho (WGP) com duas unidades de execução (CU) ou 128 processadores de fluxo. Outros componentes importantes do cIOD são a interface PCIe Gen 5 com suporte para 28 pistas, duas interfaces IFoP para interconexão com blocos principais CCD, uma E/S SoC bastante grande com suporte para USB 3.x e outros tipos de interfaces, também como uma das partes mais importantes do processador – controlador de memória DDR5 com interface de canal duplo (com quatro subcanais).