A era do atraso da Intel no número de núcleos nos processadores de servidor, iniciada pela estreia do AMD EPYC 7002 Rome há cinco anos, está gradualmente se tornando uma coisa do passado. No verão, a empresa lançou os chips Xeon 6700E (Sierra Forest) com 144 núcleos. Mas se Sierra Forest ainda pudesse ser condicionalmente considerado Xeon não muito “real” devido ao uso de E-cores exclusivamente energeticamente eficientes sem SMT, que se opõem ao AMD EPYC Bergamo de 128 núcleos baseado em Zen4c com SMT, então com o anúncio do Xeon 6900P isso não pode mais ser feito, vai dar certo. Conheça Granite Rapids-AP com 128 núcleos P de peso total!

Fonte da imagem: Intel

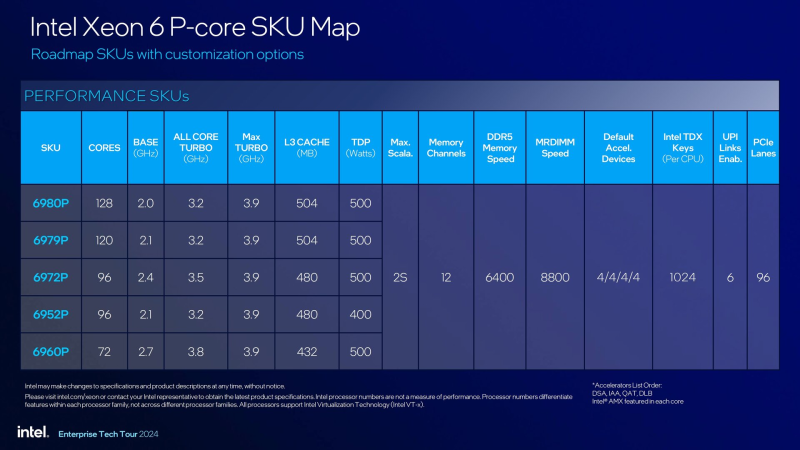

Muito sobre a arquitetura e capacidades do Granite Rapids era conhecido ainda na época do anúncio do Sierra Forest, mas agora falaremos sobre uma família completa, na qual no início cinco modelos de processadores com número de núcleos de 72 a 128 são apresentados. Neste, o novo produto mais antigo não é inferior nem mesmo ao futuro AMD EPYC Turin Dense de 128 núcleos baseado no Zen 5, cujo anúncio está prestes a acontecer.

Fonte das imagens aqui e abaixo: Intel via Phoronix/THG

Ao aproveitar núcleos sofisticados e de alto desempenho, a Intel agora é capaz de reivindicar uma vantagem de desempenho de 2,1x sobre o carro-chefe de 96 núcleos AMD EPYC Genoa em cargas de trabalho OpenFOAM e com suporte para AMX e formatos de computação específicos de IA, como FP16 em inferência- cargas de trabalho prontas, a superioridade dos cenários ResNet50 é de 5,5 vezes.

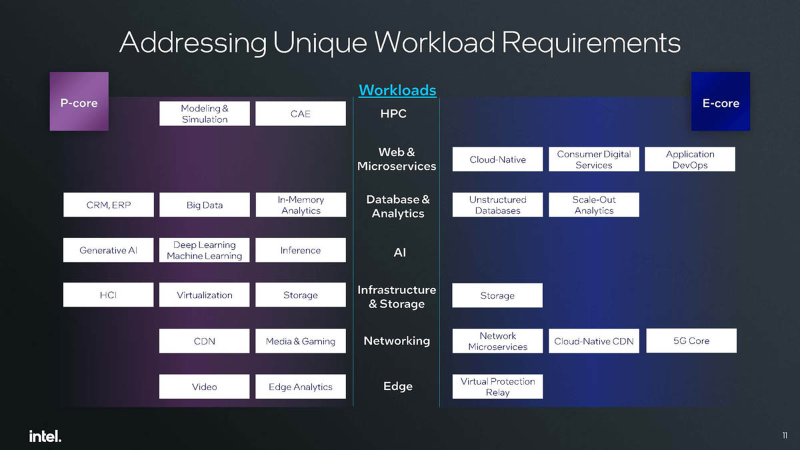

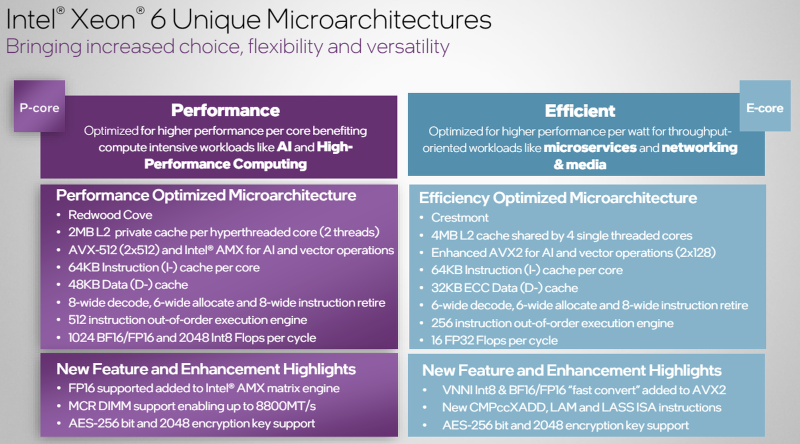

A Intel adota uma abordagem muito radical para a questão da “Grande Divisão”, distinguindo claramente as áreas ideais de aplicação para processadores com núcleos P e núcleos E, embora do ponto de vista do software a diferença não seja tão grande e na verdade resida na falta de suporte total ao AVX-512 para E-cores e AMX, que é parcialmente compensado pela implementação avançada do AVX. No entanto, a empresa não planeja lançar o Xeon com configuração mista em um futuro próximo. Observe também que os núcleos P são mais adequados nos casos em que é necessário desempenho máximo por thread, o que é especialmente importante para aplicações com licenciamento por núcleo.

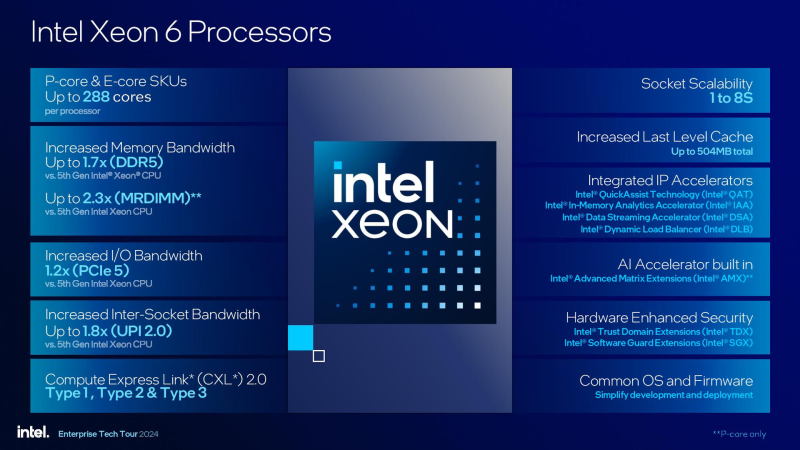

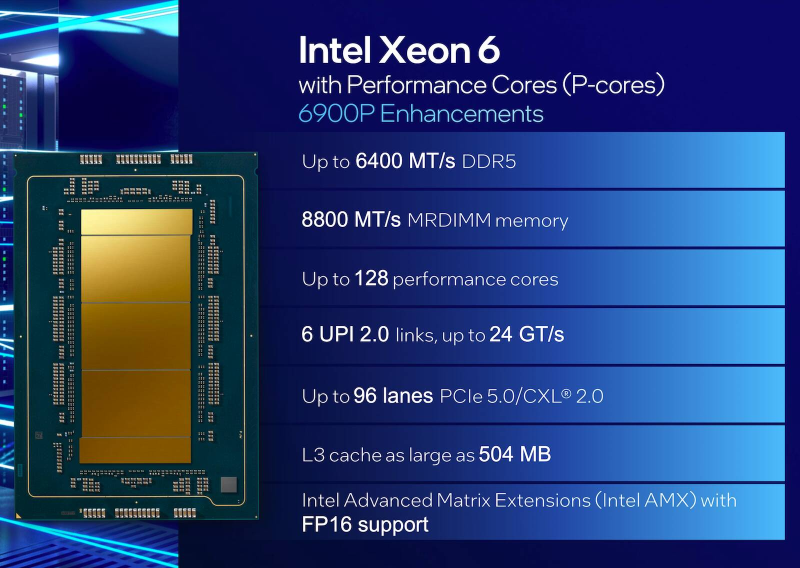

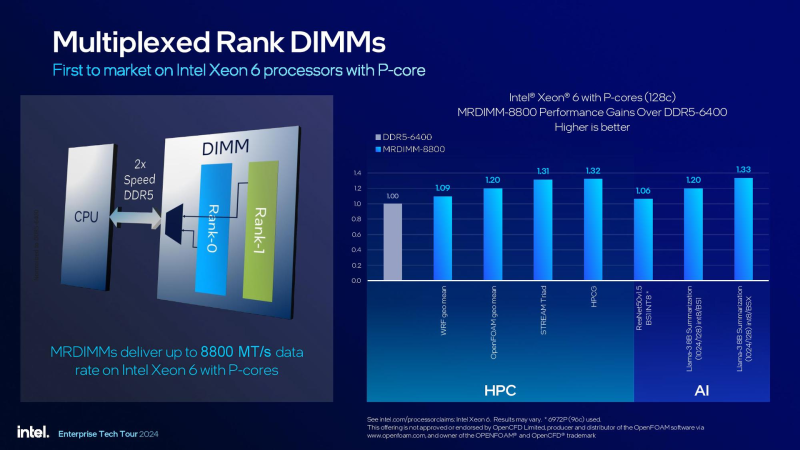

A nova série Xeon 6900P possui núcleos Redwood Cove com suporte SMT (HT), oferecendo 512 threads por sistema de processador duplo e um controlador de memória de 12 canais projetado para corresponder e superar os subsistemas de memória da AMD. Funciona com módulos DDR5-6400, mas o suporte MRDIMM permite-nos falar em velocidades de 8800 MT/s.

Os núcleos incluem duas unidades de execução para o conjunto de instruções AVX-512. O cache L1 consiste em 64 KB para instruções e 48 KB para dados. O decodificador foi projetado para processar 8 instruções por ciclo de clock, o mesmo rendimento do pipeline no processamento de microoperações. O próprio mecanismo de execução fora de ordem é duas vezes mais poderoso que o implementado em Sierra Forest e pode acomodar 512 instruções.

O volume de caches de nível superior também é impressionante: cada núcleo Redwood Cove tem seu próprio cache L2 de 2 MB, e o tamanho do cache L3 compartilhado chega a 504 MB – apenas AMD EPYC Genoa-X com 3D V-Cache pode oferecer mais. Em uma configuração de processador duplo, isso fornece mais de 1 GB de cache, o que certamente será útil em cenários de HPC e IA. Cada processador Xeon 6900P possui 96 pistas PCI Express 5.0 com suporte para CXL 2.0, cobrindo todos os tipos de dispositivos – Tipo I, II e III. Seis linhas UPI com capacidade de 24 GT/s são responsáveis pela comunicação entre processadores.

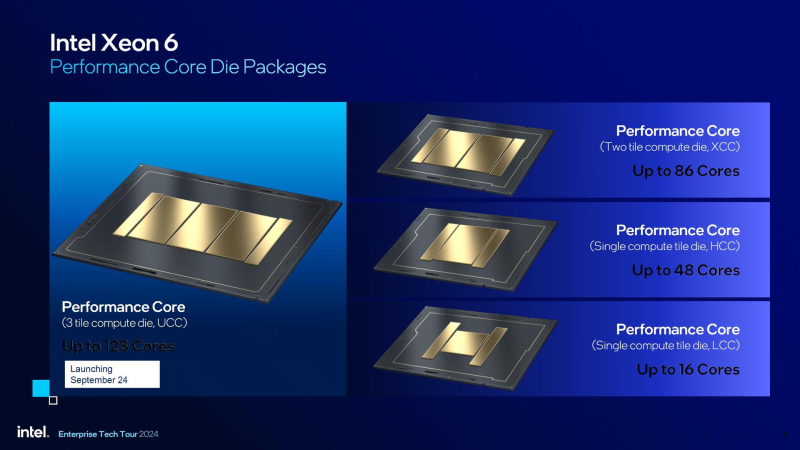

Os processadores utilizam o chamado “soquete grande” LGA 7529. Posteriormente, o Xeon 6 com P-cores será lançado para o “soquete pequeno” LGA 4710, atualmente usado pelos chips Sierra Forest, mas isso não acontecerá antes do primeiro trimestre de 2025. Serão soluções com menos núcleos (até 86) e um subsistema de memória de oito canais. Nessa altura também serão desenvolvidas soluções com E-cores em LGA 7529, mas por enquanto Sierra Forest e Granite Rapids existem exclusivamente dentro das suas plataformas.

Fonte da imagem: Intel

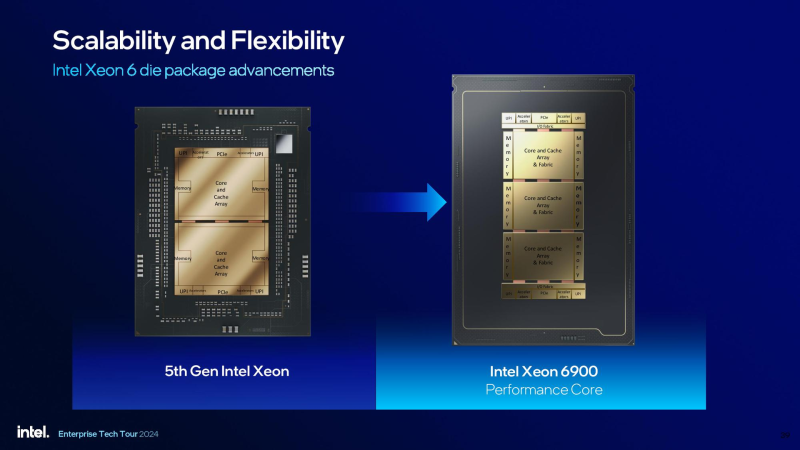

O Xeon 6900P tem um layout de chiplet, claro, que também foi abordado no teste do Xeon 6700 Porém, agora sabemos mais: na apresentação de novos produtos, a Intel mostrou que os chips com P-cores serão de dois tamanhos: LCC. (baixa contagem de núcleos), limitada a 16 núcleos, e um HCC maior (alta contagem de núcleos), contendo até 48 núcleos. A configuração XCC (eXtreme core count) é formada pelo arranjo de dois ou três chips HCC. É a última opção com três blocos usada por todos os cinco modelos Xeon 6900P.

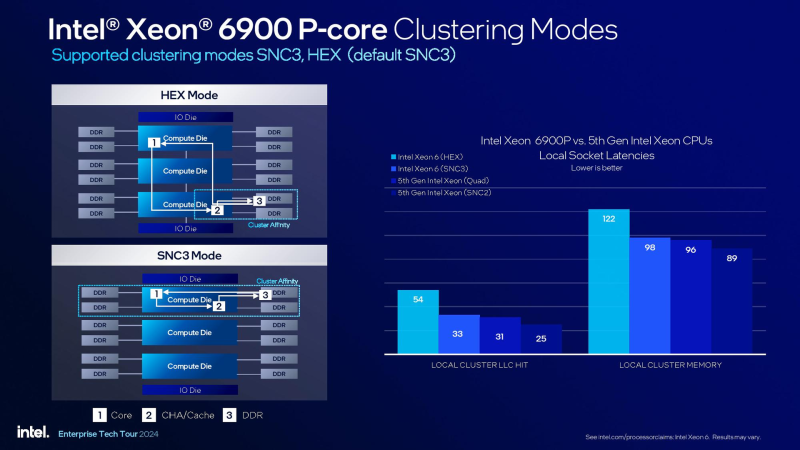

Na verdade, podemos falar do Xeon 6900P como um sistema NUMA com três nós. Como os controladores DDR5 estão localizados no processador em vez de chips de E/S como o AMD, o suporte para diferentes modos de cluster permite, em alguns cenários, beneficiar-se na latência de acesso à memória e, portanto, no desempenho. O Xeon 6900P possui dois desses modos – HEX e SNC3. Este último implementa o cenário “cada chiplet acessa seus próprios controladores DDR”.

É interessante que seja utilizada uma configuração com dois blocos com 43 núcleos ativos cada, enquanto o terceiro possui apenas 42 núcleos ativos. Isso foi feito, claro, para 128 núcleos, mas hipoteticamente nada impediu a Intel de ativar mais núcleos e obter um chip que supera o EPYC em número de núcleos. O motivo, presumivelmente, é o apetite energético dos novos produtos, que mesmo com 128 núcleos já requerem meio quilowatt.

O Xeon 6900P possui um padrão específico de latência durante a interação entre núcleos. A comunicação entre núcleos pertencentes aos chips mais externos não é caracterizada por baixas latências, o que é natural. Podemos prever com segurança latências ligeiramente mais altas quando o chiplet médio opera com dispositivos externos, uma vez que os chips de E/S estão localizados literalmente nas bordas da CPU.

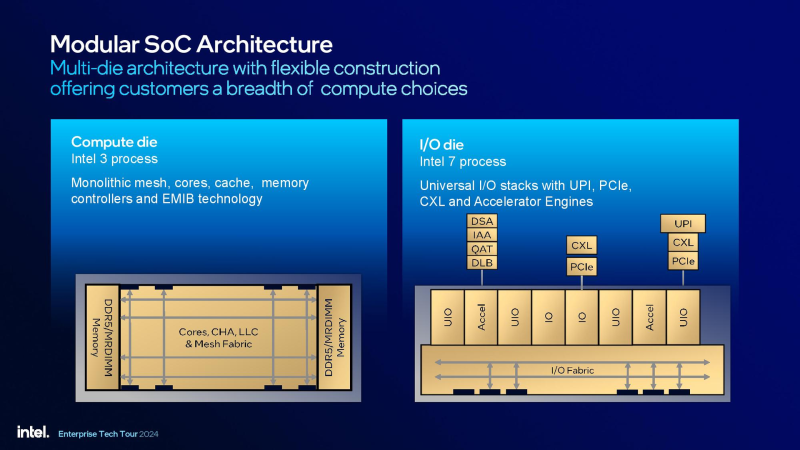

Os chips, como já foi observado repetidamente, são mais monolíticos na implementação do que os da AMD: os chips são costurados via EMIB e usam uma rede mesh modular universal. Os blocos de computação são produzidos usando a tecnologia de processo Intel 3, enquanto os chips de E/S usam o processo Intel 7, mais barato e mais difundido. Ao contrário de um módulo semelhante no AMD EPYC, eles são responsáveis apenas pela implementação de interfaces UPI/PCIe/CXL e pela comunicação com aceleradores. DSA/IAA/QAT/DLB.

A nova linha abre com o Xeon 6960P de 72 núcleos, que pode ser chamado de resposta da Intel ao NVIDIA Grace (72 núcleos no GH200, 144 núcleos no Grace Superchip). Porém, você tem que pagar por tudo e, neste caso, o retorno é o pacote de calor aumentado para 500 W. Apenas o modelo 6952P com frequência base baixa é um pouco menor e chega a 400 W. Fora isso, os 6900P são muito parecidos, eles ainda têm a mesma frequência turbo de 3,9 GHz para um único núcleo e 3,7 GHz para todos os núcleos. No momento, isso é superior ao AMD EPYC Genoa de “núcleo” semelhante. Todas as variantes possuem quatro aceleradores ativos de cada tipo, 12 canais de memória, seis pistas UPI e 96 pistas PCIe 5.0.

Vale a pena mencionar separadamente sobre a memória. O crescimento do número de canais e da capacidade de memória é muito mais lento do que o crescimento do número de núcleos. Isto é especialmente verdade à luz do boom das tecnologias de IA, que, pela sua natureza, exigem muita memória. Há também um problema com as velocidades: embora seja parcialmente melhorado pela transição para DDR5, mesmo Sierra Forrest suporta apenas DDR5-6400. Granite Rapids-AP também suporta essa memória, mas a capacidade de trabalhar com módulos MRDIMM-8800 parece mais promissora.

Externamente, os MRDIMMs (e MCR DIMMs) se assemelham aos módulos de registro DDR5 convencionais, no entanto, o uso de um buffer adicional permite que os novos módulos operem no modo de leitura de duas fileiras ao mesmo tempo, em vez de um nos DIMMs convencionais. Vale dizer que a JEDEC planeja publicar apenas a especificação MRDIMM. Até o momento, a Intel leva vantagem, mas ainda é cedo para falar em produção em massa do novo tipo de memória. Existe a possibilidade de que a implementação do suporte da AMD para esta memória seja diferente.

Fonte: Phoronix

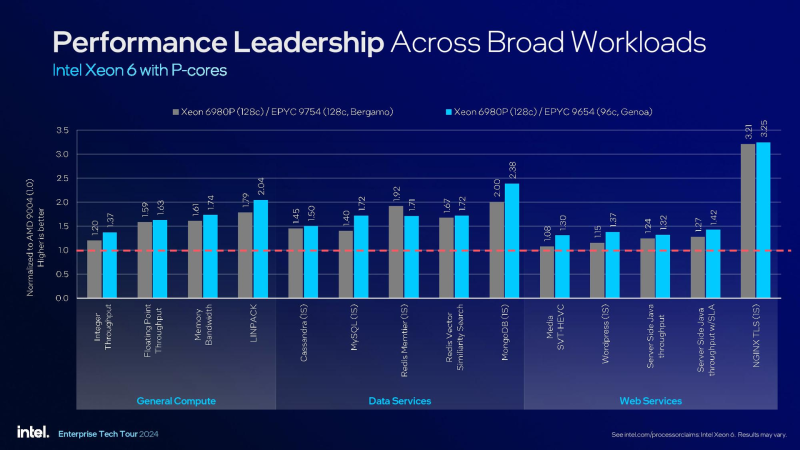

Quanto ao desempenho em geral, os primeiros resultados também já estão disponíveis: em testes realizados pelo recurso Phoronix, a plataforma equipada com dois carro-chefe Xeon 6980P conquistou com segurança o primeiro lugar, à frente dos conjuntos de processador duplo com AMD EPYC 9754, 9684X e 9654.

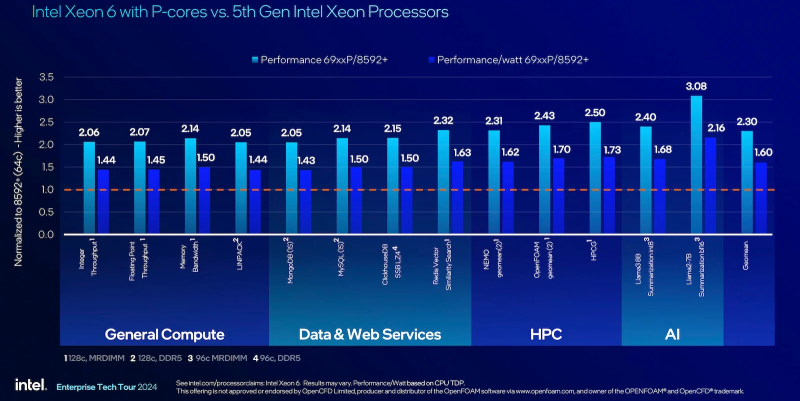

De acordo com os números fornecidos pela própria Intel, a superioridade do Xeon de sexta geração sobre a quinta (Emerald Rapids) é de 2 a 3x em desempenho puro, e em termos de watts varia de 1,44x a 2,16x, dependendo do tipo e natureza da carga. Vale ressaltar que, apesar do pacote térmico aumentado, a eficiência energética do Xeon 6900P também aumentou: com uma carga típica de servidor de 40%, os novos processadores oferecem 1,9 vezes mais desempenho por watt do que a geração anterior do Xeon.

Comparado às soluções AMD com um número comparável de núcleos (EPYC 9754 e 9654, 128 e 96 núcleos, respectivamente), o Xeon 6980P é 1,2-3,21 vezes mais rápido, com a menor vantagem manifestada no trabalho com dados inteiros, e visivelmente mais – em cálculos de ponto flutuante, bem como em testes de subsistemas de memória.

Vamos resumir os resultados intermediários. Ao mesmo tempo, a AMD conseguiu avançar no campo da criação de processadores para servidores multi-core precisamente graças à transição para um layout de chiplet. Em grande medida, o triunfo dos “vermelhos” foi facilitado pelo processo obscenamente demorado de introdução da tecnologia de 10 nm da Intel. Como resultado, durante cinco anos inteiros, o EPYC aumentou com sucesso o número de núcleos, enquanto os “azuis”, mantendo teimosamente a solidez do cristal, também foram limitados pelos parâmetros do processo técnico. Isso não nos permitiu cruzar com segurança a marca de 64 núcleos.

Fonte da imagem: Intel

Apenas Sapphire Rapids conseguiu implementar a opção de layout de chiplet. Embora desde o início tenha sido usado um princípio de costura de chips de nível inferior, até recentemente era usada a opção homogênea, não muito bem-sucedida, com grandes chips universais. E somente na geração Xeon 6 estreou uma versão heterogênea com a parte de E/S colocada em chips separados, o que, em combinação com processos técnicos sofisticados e dominados, permitiu à Intel fazer um avanço que reduziu a lacuna com a AMD.

Agora a Intel não tem apenas um trunfo na forma de arquitetura de alto desempenho e unidades aceleradoras específicas, mas também simplesmente Xeons “grandes” que podem competir em igualdade de condições com o EPYC no número de núcleos. A situação também é interessante porque no dia 10 de outubro a AMD se prepara para apresentar oficialmente o novo EPYC Turin Dense baseado no Zen 5, que também receberá 128 núcleos. Mas a AMD está preparando não apenas eles, mas também EPYC de 192 núcleos baseado no Zen 5c. E como sabemos, às vezes a quantidade supera a qualidade.