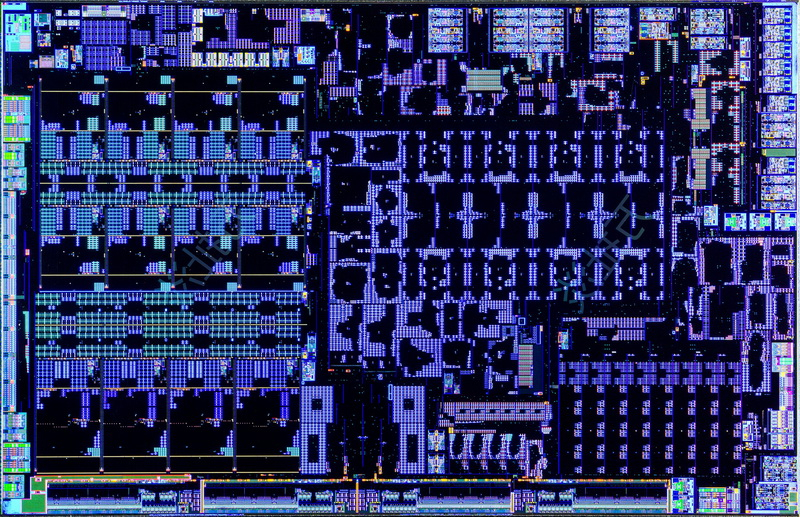

Os entusiastas publicaram uma imagem detalhada da matriz de 4 nm do novo processador móvel AMD Strix Point (Ryzen AI 300), na qual todos os componentes do chip são claramente visíveis. Junto com a imagem havia uma descrição detalhada de quais componentes estavam contidos no chip.

Fonte da imagem: Bilibili

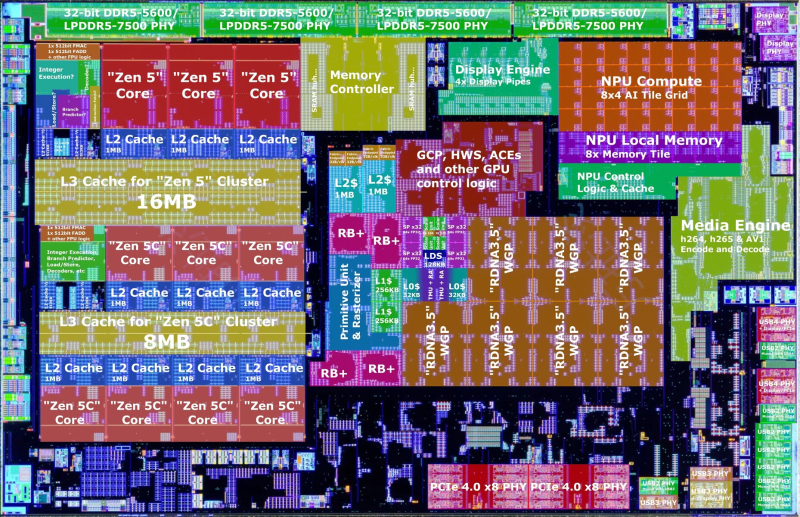

O novo Strix Point é significativamente maior que o cristal Phoenix – suas dimensões são 12,06 × 18,71 mm contra 9,06 × 15,01 mm do chip da geração anterior. O aumento na área se deve principalmente ao fato de o Strix Point ter recebido unidades maiores de CPU, iGPU e NPU. Além disso, a AMD transferiu a matriz do novo chip da tecnologia de processo TSMC N4 (Phoenix e seu sucessor Hawk Point) para a tecnologia de processo aprimorada TSMC N4P.

O novo processador possui 12 núcleos de computação, divididos em dois blocos CCX, um dos quais contém quatro núcleos Zen 5 e 16 MB de cache L3, e o segundo contém oito núcleos Zen 5c com eficiência energética e 8 MB de cache L3 dedicados a eles. Os blocos CCX são conectados ao restante do processador por meio de um barramento Infinity Fabric. Uma unidade iGPU muito grande ocupa a parte central do chip. É baseado na arquitetura gráfica RDNA 3.5 e contém oito processadores de grupo de trabalho (WGP) ou 16 unidades de execução (CU), que incluem 1.024 processadores de fluxo. Outros componentes importantes do iGPU incluem quatro unidades de renderização com 16 ROPs e lógica de controle. A placa gráfica Strix Point integrada possui seus próprios 2 MB de cache L2.

Fonte da imagem: X/@GPUsAreMagic

Ao lado do iGPU, no lado direito da matriz Strix Point, estão seus componentes irmãos, o Media Engine e o Display Engine. O primeiro fornece aceleração de hardware para codificação e decodificação de h.264, h.265 e AV1, bem como vários formatos de vídeo legados. O Display Engine é responsável por codificar o quadro de saída do iGPU em vários formatos de conector (como DisplayPort, eDP, HDMI), incluindo compressão de fluxo acelerada por hardware (DSC). Os circuitos Display PHY são responsáveis pela camada física de conexão do iGPU aos conectores de vídeo.

O NPU é o terceiro componente lógico chave do Strix Point. Os novos processadores AMD usam a segunda geração de NPUs, cujas dimensões físicas tornaram-se visivelmente maiores que as do Phoenix. A nova NPU é baseada na arquitetura avançada XDNA 2 e contém 32 blocos de mecanismo de IA que interagem com sua própria memória local de alta velocidade e lógica de controle, que por sua vez está conectada ao barramento Infinity Fabric. Este NPU foi projetado para atender aos requisitos do ecossistema Copilot Plus PC da Microsoft e oferece desempenho de 50 TOPS (trilhões de operações por segundo).

O controlador de memória no Strix Point suporta DDR5-5600 de canal duplo (160 bits) e RAM LPDDR5 de 128 bits com velocidades de até 7500 MT/s. O controlador tem um tamanho de cache SRAM não especificado, que também foi visto em Phoenix 2 e Phoenix morre.

A matriz Strix Point tem um complexo de raiz PCIe menor que o Phoenix, que por sua vez é menor que a matriz Cezanne (Ryzen 5000). Nas últimas três gerações de processadores, a AMD reduziu o número de pistas PCIe em quatro. Se Cezanne tiver 24 pistas PCIe 3.0 (x16 para placa de vídeo + x4 para SSD NVMe + x4 para barramento de chipset ou GPP), então Phoenix terá o número de pistas reduzido para 20 PCIe 4.0 (x8 para placa de vídeo + x4 para SSD NVMe + x4 para barramento de chipset ou GPP+x4 para USB4). E o novo Strix Point tem o número de pistas PCIe 4.0 reduzido para 16 (x8 para placa de vídeo + x4 para SSD NVMe + x4 para USB4 ou GPP).

A redução no número de pistas PCIe se deve ao fato do Strix Point ser projetado para competir com o Intel Lunar Lake, que também possui apenas quatro pistas PCIe por placa gráfica ou GPP. Com o lançamento dos processadores Arrow Lake-H e Arrow Lake-HX da Intel, espera-se que a AMD lance chips Fire Range que contarão com 28 pistas PCIe 5.0 e podem ser emparelhados até mesmo com as GPUs móveis discretas mais rápidas.