A TSMC na produção de aceleradores de computação exigidos pelo mercado, a NVIDIA usa seus próprios recursos para empacotamento espacial de chips (CoWoS), mas com o aumento da demanda, eles não eram mais suficientes, então a gigante taiwanesa partiu para a expansão. Até o final do próximo ano, eles devem ser duplicados, segundo fontes bem informadas.

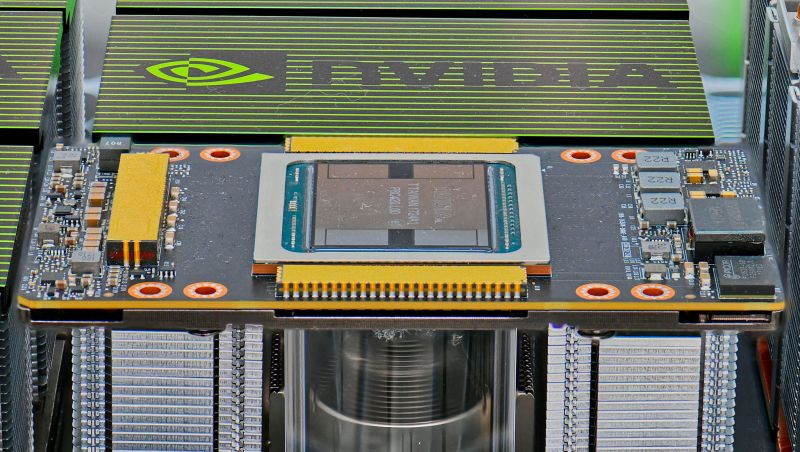

Fonte da imagem: NVIDIA

Sobre os planos relevantes ficaram conhecidos com o arquivamento da edição taiwanesa do DigiTimes, que se refere ao recurso Tom’s Hardware. Atualmente, a própria capacidade de empacotamento de chips CoWoS da TSMC não pode processar mais de 8.000 wafers de silício por mês. Até o final deste ano, os volumes serão aumentados para 11.000 wafers de silício por mês, e até o final do próximo ano, para todos os 16.000 no cenário mais otimista. Os primeiros rumores mencionavam os planos da TSMC de aumentar os volumes para 20.000 placas por mês até o final de 2024, mas em um mercado volátil, esses ajustes são possíveis de uma forma ou de outra.

Os clientes da TSMC nesta área, além da NVIDIA, são Amazon (AWS), Broadcom, Cisco e Xilinx (AMD). Agora, a TSMC, de acordo com a mídia taiwanesa, está comprando ativamente os equipamentos necessários para expandir sua capacidade de empacotamento de chips usando o método CoWoS. Alega-se que a NVIDIA já reservou cerca de 40% do programa de produção da TSMC para o próximo ano nesta área. O desenvolvedor de chips americano ainda teve que procurar contratados adicionais na pessoa da Amkor Technology e da UMC para atender a esses pedidos, mas até agora eles não podem ajudar muito devido às suas capacidades limitadas.

Por sua vez, os fornecedores da TSMC devem entregar cerca de 30 conjuntos de equipamentos especializados até meados do ano que vem para que a empresa concretize seus planos de expansão da capacidade envolvida no empacotamento de chips pelo método CoWoS. Ao mesmo tempo, a TSMC está otimizando suas próprias instalações de produção para aumentar mais rapidamente os volumes de processamento de chips nessa área. Na semana passada, a TSMC abriu o Fab 6, que se concentrará no teste e embalagem de chips, incluindo o método CoWoS.

A NVIDIA usa o layout CoWoS na produção dos aceleradores A100, A30, A800, H100 e H800, que agora são muito procurados por desenvolvedores de sistemas de inteligência artificial. No caso da AMD, um layout semelhante é usado na produção dos aceleradores de computação Instinct dos modelos MI100, MI200, MI250X e do futuro MI300. Deste ponto de vista, os planos da TSMC para expandir as capacidades principais são de grande importância para os negócios da NVIDIA, AMD e outros grandes clientes.