Não é segredo que o desenvolvimento futuro da microeletrônica está no plano de amontoar diferentes cristais uns sobre os outros na forma de embalagens 3D. Para a ampla promoção desse conceito, era necessário um instrumento para teste independente de cristais em pilhas. Agora existe essa ferramenta.

O Imec, um centro de pesquisa belga, anunciou recentemente que a IEEE Standards Association aprovou recentemente o padrão IEEE Std 1838. Em fevereiro, toda a documentação para o novo padrão aparecerá na biblioteca digital IEEE Xplore, de onde pode ser obtida. A abreviação Std, no nome do padrão, significa design para teste ou, em russo, design (desenvolvimento) para o teste.

O lançamento do desenvolvimento do padrão foi iniciado pelo Imec e começou em 2011. A princípio, o grupo de trabalho era liderado por um representante do centro belga e, nos últimos anos, o trabalho foi liderado por um dos desenvolvedores seniores da Cadence. Como vemos, foram necessários quase 9 anos para desenvolver o padrão IEEE Std 1838.

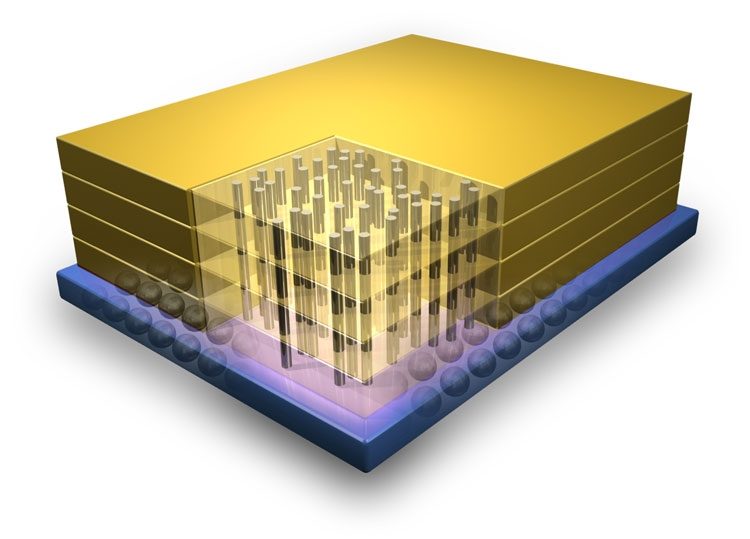

A necessidade do padrão IEEE Std 1838 surgiu porque o setor não possuía um único mecanismo para testar pilhas de vários empilhados em uma coluna de cristais. Enquanto isso, muitas opções foram inventadas para a montagem vertical de cristais em pilhas, e os cristais precisam poder testar separadamente, no estágio da montagem parcial, o campo para a montagem completa e após a conclusão da embalagem. Obviamente, a abordagem “quem está na floresta, quem está perto do fogo” pode colocar designers, fabricantes e clientes em uma posição desconfortável.

Através dos esforços de uma equipe de engenheiros, o padrão IEEE Std 1838 permite que cada chip seja testado em uma pilha montada usando ferramentas universais e um sistema de comando. Tanto o cliente quanto o desenvolvedor poderão operar com os mesmos conjuntos de ferramentas para testar a operacionalidade de cada nível em um chip de multicamadas.

O acesso a cada chip na pilha está disponível através de um conector de teste padrão ou usando sondas de agulha padrão no equipamento de teste. A arquitetura IEEE Std 1838 e a interface de sinalização incluem três componentes. O registro do shell de cristal (DWR, registro do invólucro da matriz), o mecanismo de controle serial (SCM, mecanismo de controle serial) e a porta paralela flexível opcional (FPP, porta paralela flexível).

Somente a porta FPP opcional tornou-se completamente nova. Este é um mecanismo de acesso multi-bits escalonável para testes com troca massiva de dados com cada camada (cristal). O registro DWR e o mecanismo SCM já são usados nos padrões atuais marcados como Padrão. O primeiro fornece testes em nível de unidade do cristal em seu nível e varre as correntes nos limites do cristal acima e abaixo. O segundo é a transferência de comandos de controle de um bit para cada nível durante o processo de teste. Todos juntos prometem acelerar a entrada no mercado de soluções multi-chip com um arranjo vertical de cristais. Especialmente quando o novo padrão será implementado em sistemas de design automático.

.