Como sabemos, a transição para uma tecnologia de processo de 3 nm será acompanhada por uma transição para uma nova arquitetura de transistor. Em termos da Samsung, por exemplo, serão transistores MBCFET (Multi Bridge Channel FET), nos quais o canal do transistor se parecerá com vários canais localizados um acima do outro na forma de nanopáginas cercadas por uma porta em todos os lados (para obter mais detalhes, consulte no arquivo de nossas notícias de 14 de março).

A estrutura do transistor de 3 nm Samsung MBCFET

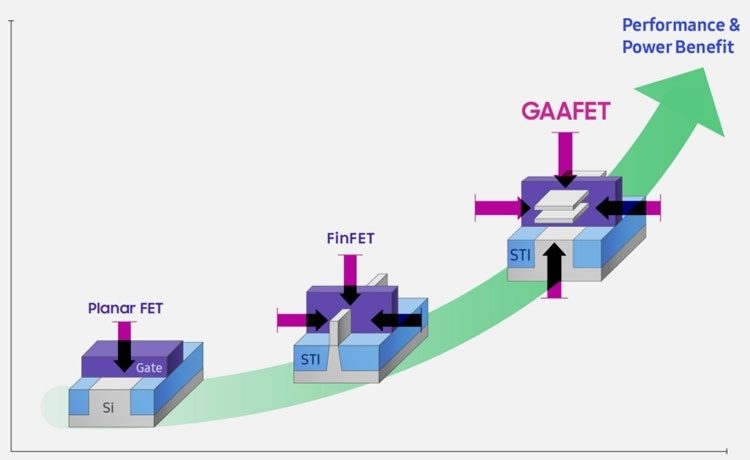

De acordo com desenvolvedores do centro belga Imec, essa é uma estrutura de transistor progressiva, mas não ideal, usando portas verticais FinFET. Ideal para processos industriais com uma escala de elementos inferior a 3 nm seria uma estrutura de transistor diferente da proposta pelos belgas.

A Imec desenvolveu um transistor de página dividida ou Forksheet. São as mesmas nanopáginas verticais dos canais dos transistores, mas separadas por um dielétrico vertical. Um transistor com um canal n é criado por um lado do dielétrico e um canal p por outro. E os dois estão rodeados por um obturador comum na forma de uma nervura vertical.

A Imec oferece um transistor com nanopáginas separadas (Forksheet)

Reduzir a distância no chip entre transistores com condutividade diferente é outro grande desafio para reduzir ainda mais a escala do processo. A simulação do TCAD confirmou que um transistor de página dividida fornecerá uma redução de 20% na área do chip. Em geral, a nova arquitetura de transistor reduzirá a altura da célula lógica padrão para 4,3 faixas. A célula se tornará mais simples, o que também se aplica à fabricação de uma célula de memória SRAM.

Evolução da célula lógica como canais com portas verticais melhoram

Uma transição simples de um transistor em nanoescala para um transistor com páginas separadas em nanoescala proporcionará um aumento de 10% na produtividade enquanto conserva o consumo ou uma redução de 24% no consumo sem um aumento na produtividade. A modelagem para a tecnologia de processo de 2 nm mostrou que a célula SRAM usando nanofios separados fornecerá uma redução combinada na área e aumentará a produtividade em até 30% quando as transições p e n estiverem espaçadas a 8 nm.

.